FLI R

ADK

Ge tt in g S ta rt ed

The information contained herein does not contain technology as

defined by EAR,15 CFR772, is publicly available, and therefore

not subject to EAR.

15

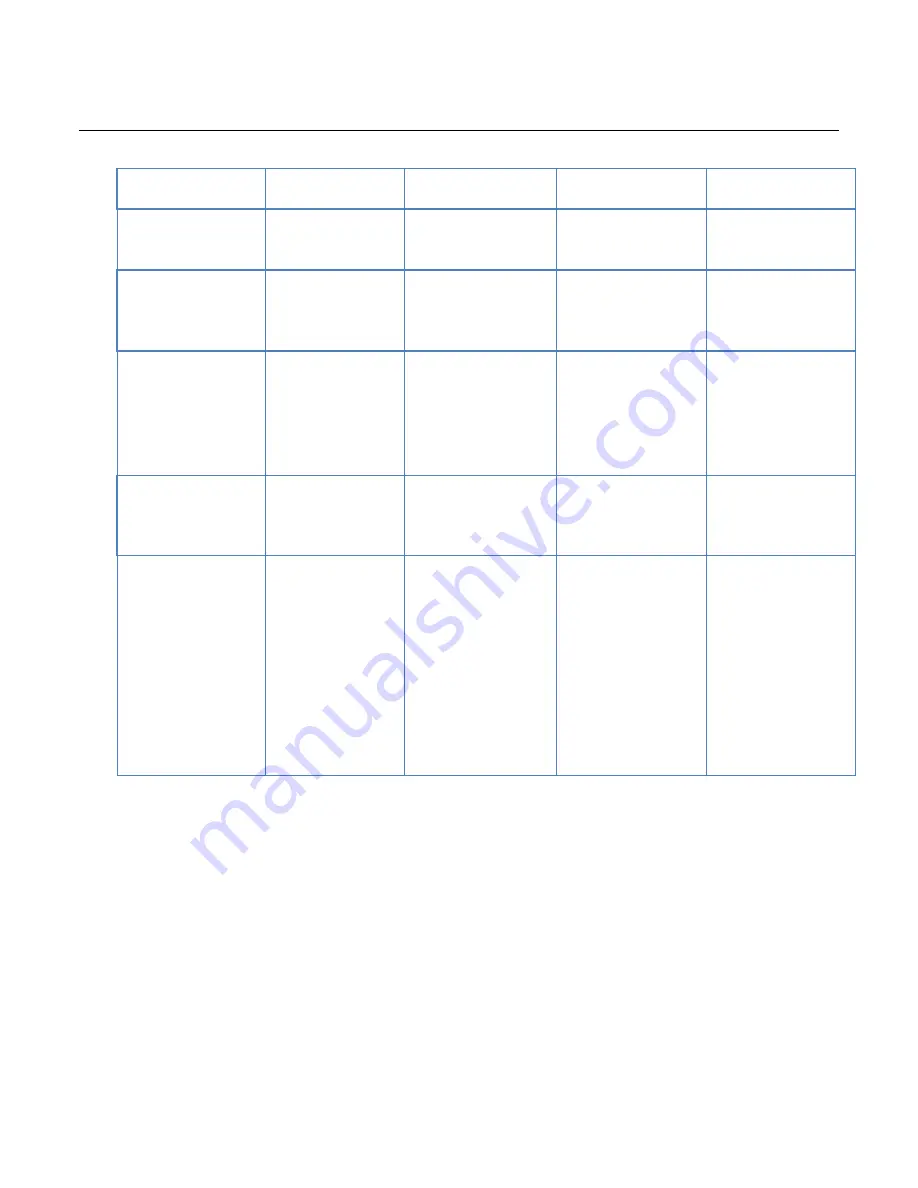

Frame Acq

Boson ROIC Sync

Received

Boson ROIC

Frame Acq Start

288 us

Frame Acq

Boson ROIC Frame

Acq Start

Boson ROIC Frame

Acq Complete

16.4 ms

The time it takes to

read out a full

frame.

Image Frame

Standard Image

Processing 16-bit

Start

Standard Image

processing 16-bit

complete

8.6 ms

NUC, Lagrange, DPR,

SCF

Image Frame

Additional Image

Processing (AGC)

Start

Additional Image

Processing (AGC)

Complete

17 ms

Auto Gain

Correction, Contrast

Enhancement,

Frame, conversion

to 8-bit

(*this step is

optional)

Image Frame

Image Processing

Complete

CMOS start of frame

transmission

128 us

Image Frame

CMOS - Serializer

Start of frame

transmission

Deserializer

–

Mipi

Complete frame

transmission

(16.67 ms) CMOS

output frame

transmission

(~10 us) SerDes

data transmission

(depending on cable

length.)

The time it takes

from when CMOS

output on the Boson

starts and MIPI

output from the

Deserializer

Completes frame

data transmission

The GMSL signal pipeline introduces very little additional latency compared to the intrinsic

latency of the Boson frame readout, image processing, and CMOS data output. The latency

of the Boson core of the ADK is shown below for different image processing configurations.

The latency reported here is defined as the time between when the Boson receives the

external sync pulse and the time when the data transmission out of the CMOS output is

complete. The lowest latency configuration is the 16-bit pre-AGC 60 Hz output shown in

Figure 3 with a latency of ~42 ms. Turning the averager on to reduce the frame rate to 30

Hz increases the latency to ~59 ms, shown in Figure 4. Turning on the Auto Gain Correction

algorithms and outputting 8-bit pixel data at 60 Hz has a latency of ~59 ms, shown in

Figure 5. Turning on Averaging in the 8-bit pixel output increases the latency to ~75 ms,

shown in Figure 6.