FinePix S5800/S800 Service Manual

3-1

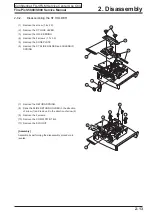

3. Schematics

Confidential: FUJIFILM Service Center Use Only

3. Schematics

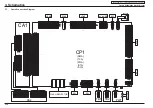

3-1.

Description of CCD circuit

operation

3-1-1.

Overview

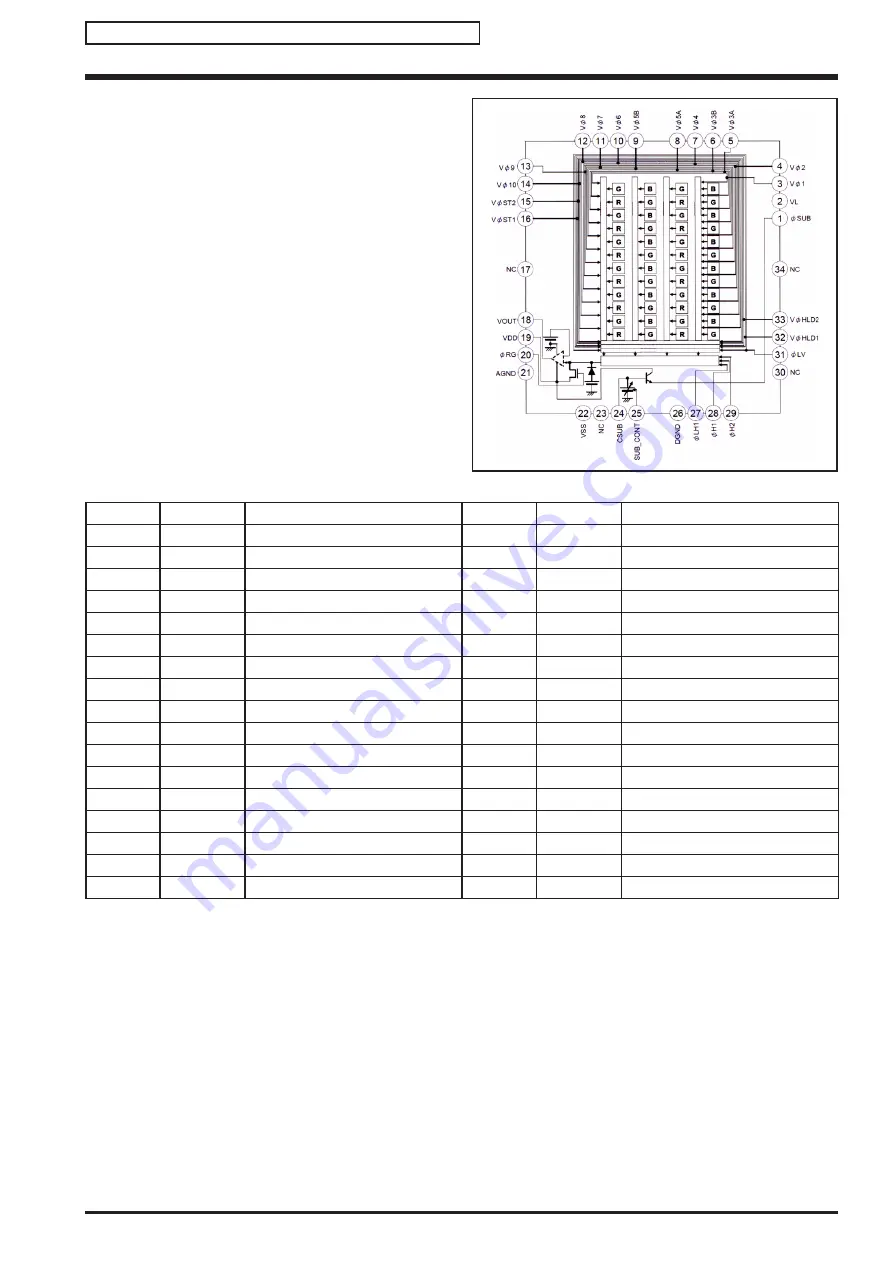

The CCD peripheral circuit block is primarily made up of the

following ICs:

IC931 (ICX646COZ) CCD imager

IC905 (AD9971BCPZRL) H driver, CDS, AGC and A/D

converter

IC901 (CXD3445GA) V driver

3-1-2.

IC931 (CCD imager)

• Interline CCD image sensor

• Image size: 7.183 mm diagonal (1/2.5-inch)

• Total pixels: 3336 x 2484 (H x V)

• Recorded pixels: 3264 x 2448 (H x V)

<Fig 3-1. CCD block diagram>

Terminal No. Terminal symbol

Terminal description

Terminal No. Terminal symbol

Terminal description

1

ØSUB

Board clock

18

V

OUT

Signal output

2

V

L

Protective transistor bias

19

V

DD

Circuit power supply

3

VØ

1

Vertical resister transfer clock

20

ØRG

Reset gate clock

4

VØ

2

Vertical resister transfer clock

21

AGND

GND

5

VØ

3A

Vertical resister transfer clock

22

VSS

GND

6

VØ

3B

Vertical resister transfer clock

23

NC

NC

7

VØ

4

Vertical resister transfer clock

24

CSUB

Board bias

8

VØ

5A

Vertical resister transfer clock

25

SUB_CONT Board biasc control

9

VØ

5B

Vertical resister transfer clock

26

DGND

GND

10

VØ

6

Vertical resister transfer clock

27

ØLH1

Horizontal resister transfer clock

11

VØ

7

Vertical resister transfer clock

28

ØH1

Horizontal resister transfer clock

12

VØ

8

Vertical resister transfer clock

29

ØH2

Horizontal resister transfer clock

13

VØ

9

Vertical resister transfer clock

30

NC

NC

14

VØ

10

Vertical resister transfer clock

31

ØLV

Vertical-horizontal sift clock

15

VØ

ST2

Vertical storage control 2

32

VØ

HLD1

Vertical signal hold 1

16

VØ

ST1

Vertical storage control 1

33

VØ

HLD2

Vertical signal hold 2

17

NC

NC

34

NC

NC

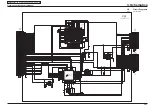

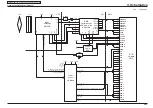

<Table 3-1. Explanation of the CCD terminals>

Horizontal register

Vertical register