54

54

54

54

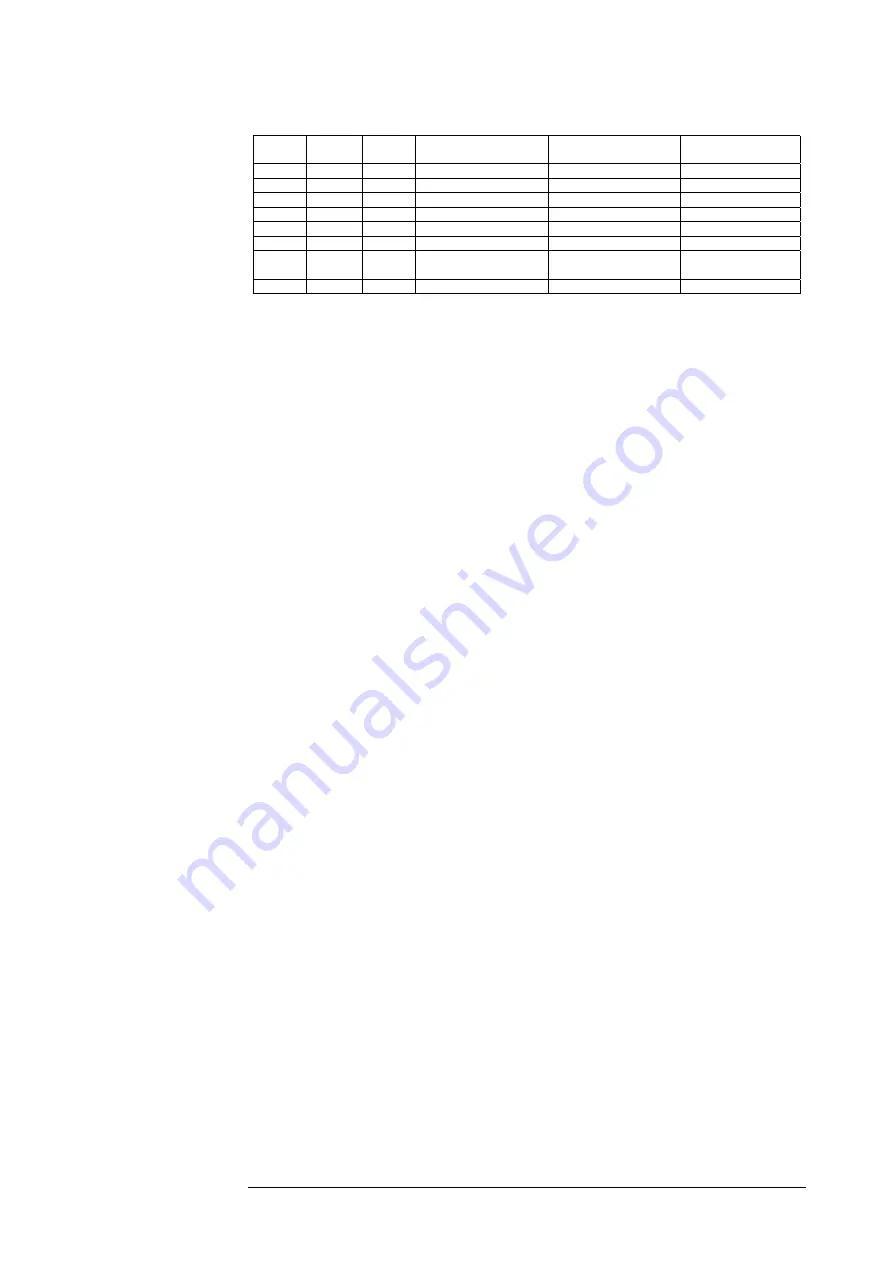

UMD2

UMD1

UMD0

Mode name

Reset vector area

External data bus

witdth

ON

ON

ON

External vector mode 0

External

8

ON

ON

OFF

External vector mode 1

External

16

ON

OFF

ON

External vector mode 2

External

16

ON

OFF

OFF

Internal vector mode

Internal

(Mode data)

OFF

ON

ON

Reserved

OFF

ON

OFF

Reserved

OFF

OFF

ON

Async serial

programming

OFF

OFF

OFF

Reserved

*When FPGA detects this setting, it sets the logic levels on the CPU port P0 in the way that P00 and P01 pins of the

CPU are pulled to ‘0’. This invokes the asynchronous serial programming mode of the CPU.

4:FLASH8/16

- If this switch is ON, the external FLASH memory interface is

configured to 16 bit mode.

5:ADR/IO

- If this switch is ON, the A16-A23 CPU pins can be switched to

general I/O mode. Any memory access above the 00FFFFh address is mirrored

to the 4000h-FFFFh area. The decode logic (FPGA) ignores the A16-A23

address signals and the MirrorFF bit setting. This switch allows to use the port

P2 (A16-A23 signals) as general I/O without giving up the external

RAM/FLASH memory. It can be useful for developing mixed mode

applications with only one 64k external RAM memory bank, that need more I/O

pins than the CPU would provide with all the external bus pins used.

Note: This is not mirroring function similar to CPU one. To control

Mirror please see The Main board Programmers reference bit MirrorFF

in System Configuration Register.