159

CHAPTER 8 16-BIT RELOAD TIMER

■

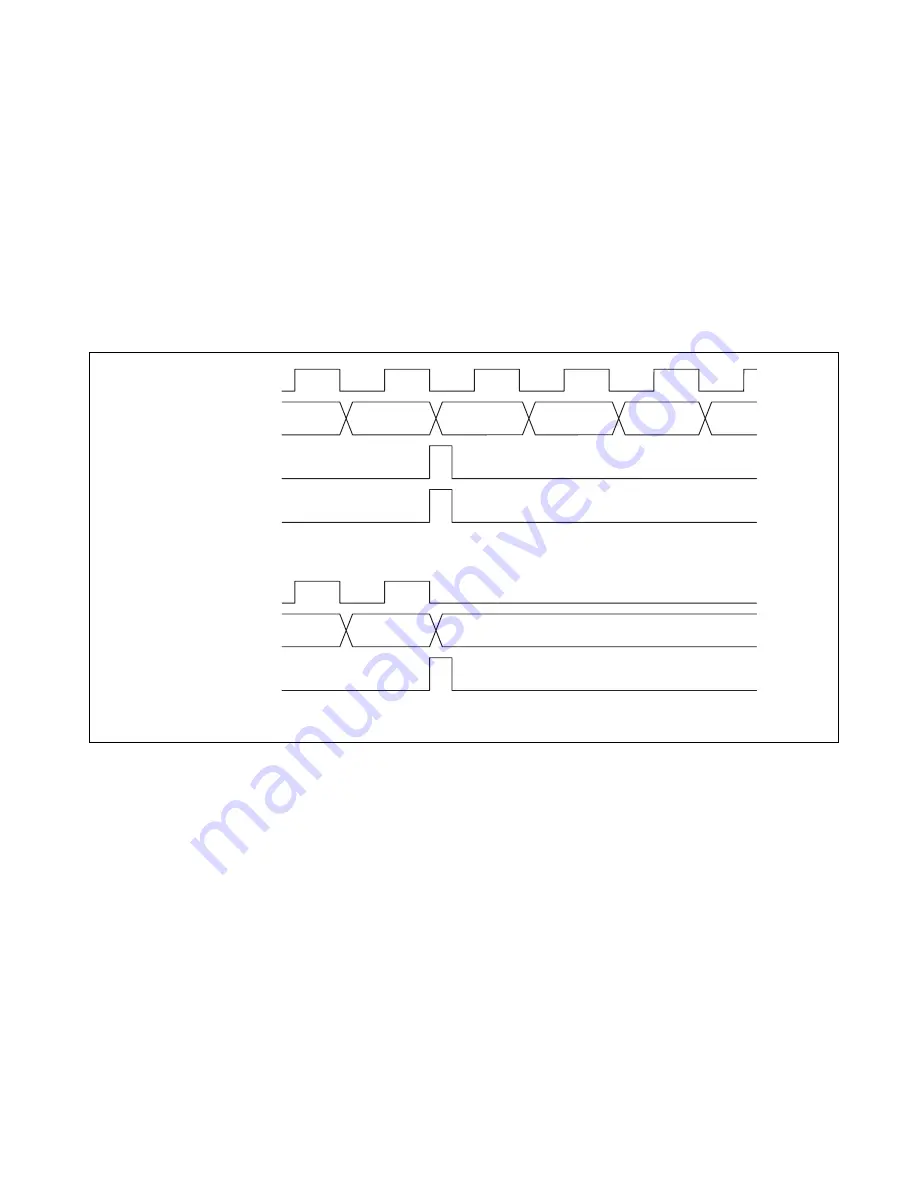

Underflow Operation

This timer defines an underflow as an event in which the counter value changes from "0000

H

" to "FFFF

H

".

Thus, an underflow occurs at the count of [Reload register setting value + 1].

If the RELD bit of the control status register is set to "1" when an underflow occurs, the contents of the

reload register are loaded into the counter and the count operation is continued. If the RELD bit is set to

"0", the counter stops at "FFFF

H

".

When an underflow occurs, it sets the UF bit of the control status register. If the INTE bit is set to "1" at

this time, it generates an interrupt request.

Figure 8.4-2 shows the operation when an underflow occurs.

Figure 8.4-2 Underflow Operation

Counter

0000

H

-1

-1

-1

Data load

Underflow set

[RELD=1]

Reload data

Count clock

Counter

Underflow set

0000

H

FFFF

H

[RELD=0]

Count clock

Summary of Contents for FR60Lite

Page 3: ......

Page 5: ......

Page 115: ...100 CHAPTER 3 CPU AND CONTROL UNITS ...

Page 127: ...112 CHAPTER 4 I O PORTS ...

Page 143: ...128 CHAPTER 5 INTERRUPT CONTROLLER ...

Page 155: ...140 CHAPTER 6 EXTERNAL INTERRUPT AND NMI CONTROLLER ...

Page 197: ...182 CHAPTER 9 PPG Programmable Pulse Generator ...

Page 337: ...322 CHAPTER 13 UART ...

Page 417: ...402 CHAPTER 16 DMAC DMA Controller ...

Page 445: ...430 CHAPTER 17 FLASH MEMORY ...

Page 451: ...436 CHAPTER 18 SERIAL PROGRAMMING CONNECTION ...

Page 493: ...478 APPENDIX F Precautions on Handling ...

Page 494: ...479 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Page 507: ...492 INDEX ...

Page 509: ......