417

CHAPTER 17 FLASH MEMORY

●

Read/Reset Command

To return to read mode after the time limit is exceeded, a read/reset command sequence will be issued.

Data is read from flash memory in the read cycle. The flash memory remains in reading state until another

command is entered.

When the power is turned on, flash memory is automatically set to the read/reset state. In this case, data can

be read without a command of the automatic algorithm.

●

Program (Write)

In CPU programming mode, data is basically written in halfword units. The write operation is performed

in four cycles of bus operation. The command sequence has two "unlock" cycles, which are followed by a

write setup command and a write data cycle. Writing to the memory starts in the last write cycle.

After an automatic write algorithm command sequence was executed, it becomes unnecessary to control the

flash memory externally. The flash memory itself internally generates write pulses to check the margin of

the cells to which data is written. The data polling function compares bit7 of the original data with bit7 of

the written data, and if these bits are the same, the automatic write operation ends (see "

Sequence Flag" in section "17.5 Automatic Algorithm Execution Status"). The automatic write operation

then returns to the read mode and accepts no more write addresses. After that, the flash memory requests

the next valid address. In this manner, the data polling function indicates the memory is in a write

operation.

During a write operation, all commands written to the flash memory are ignored. If a hardware reset starts

during write operation, the data at the address for writing may become invalid. Writing operations can be

performed in any address sequence and outside of sector boundaries. However, write operations cannot

change a data item "0" to "1". If a "0" is overwritten with a "1", either the data polling algorithm

determines that the elements are defective, or it looks as if "1" has been written. In the latter case, however,

the respective data item is read as "0" in reset/read mode. A data item "0" can be changed to "1" only by an

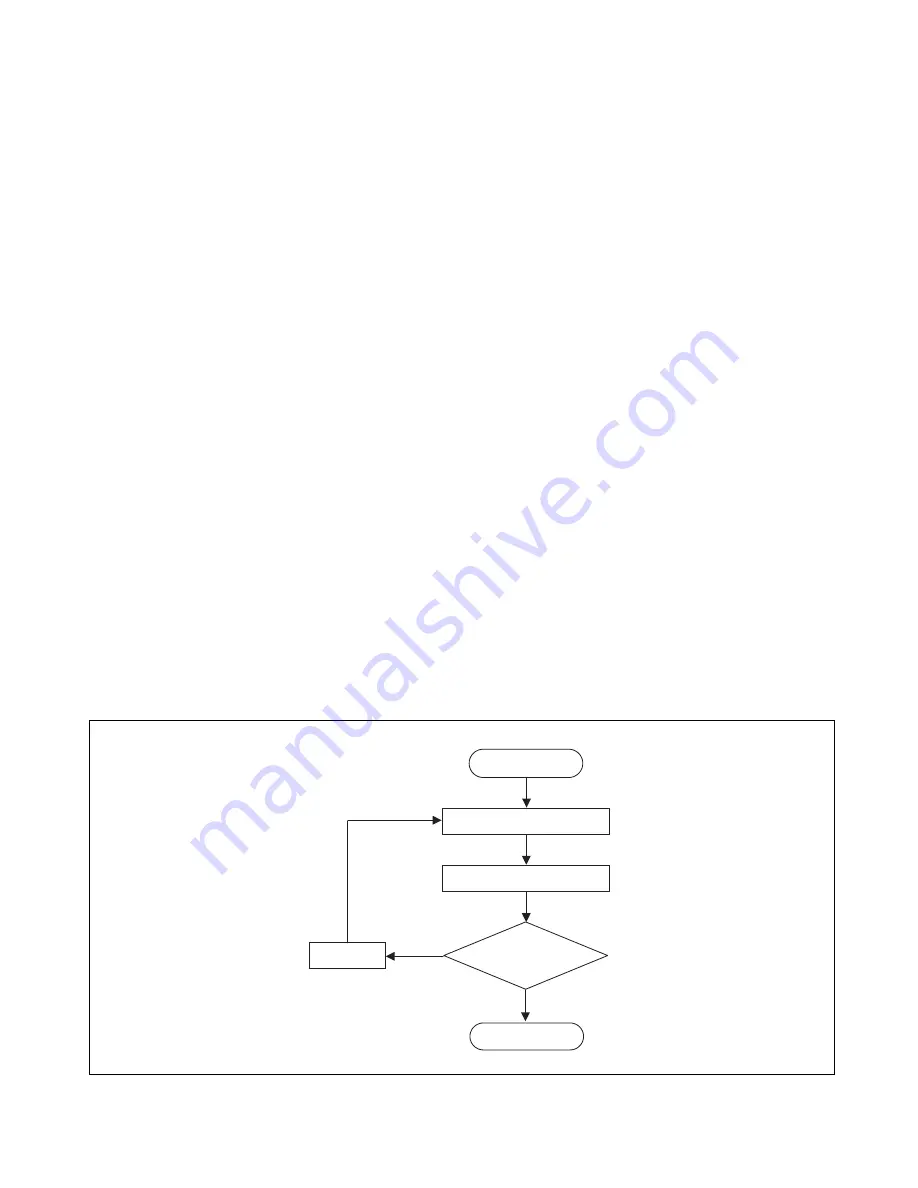

erase operation. Figure 17.4-1 shows a writing sequence with using write command.

Figure 17.4-1 Writing Sequence with Using Write Command

Write

s

t

a

rt

s

Write comm

a

nd

s

e

qu

ence

D

a

t

a

polling of the device

L

as

t

a

ddre

ss

?

Write end

s

Next

a

ddre

ss

NO

YE

S

Summary of Contents for FR60Lite

Page 3: ......

Page 5: ......

Page 115: ...100 CHAPTER 3 CPU AND CONTROL UNITS ...

Page 127: ...112 CHAPTER 4 I O PORTS ...

Page 143: ...128 CHAPTER 5 INTERRUPT CONTROLLER ...

Page 155: ...140 CHAPTER 6 EXTERNAL INTERRUPT AND NMI CONTROLLER ...

Page 197: ...182 CHAPTER 9 PPG Programmable Pulse Generator ...

Page 337: ...322 CHAPTER 13 UART ...

Page 417: ...402 CHAPTER 16 DMAC DMA Controller ...

Page 445: ...430 CHAPTER 17 FLASH MEMORY ...

Page 451: ...436 CHAPTER 18 SERIAL PROGRAMMING CONNECTION ...

Page 493: ...478 APPENDIX F Precautions on Handling ...

Page 494: ...479 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Page 507: ...492 INDEX ...

Page 509: ......