12

■

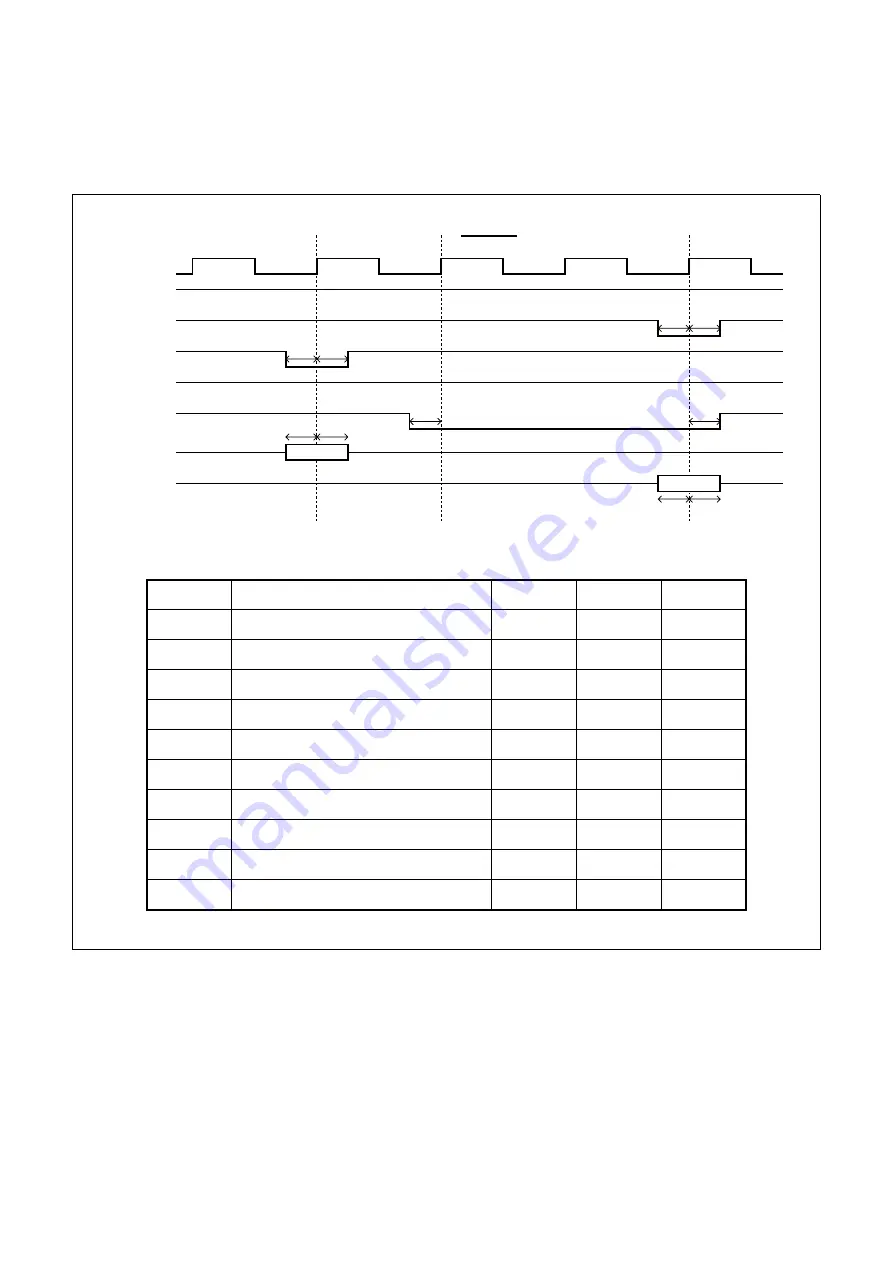

DSU-side Trace Memory Read Timing

Figure 10 shows the trace memory read timing as viewed from the DSU side.

Note that the AC specifications vary depending on the voltage applied to VCC5.

Figure 10 DSU-side trace memory read timing

TEMUL

TRDYX

TAD[27:0]

TWRX

TOEX

TDT[6

3

:0]

TAD

S

CX

TCLK

(1)

(2)

(5)

(

3

)

(4)

(6)

(7)

(8)

(9) (10)

Addre

ss

D

a

t

a

READ

Symbol

Description

Min

Max

Units

(1)

TADSCX setup time

3

-

ns

(2)

TADSCX hold time

3

-

ns

(3)

Address setup time

3

-

ns

(4)

Address hold time

3

-

ns

(5)

TOEX setup time

3

-

ns

(6)

TOEX hold time

3

-

ns

(7)

TRDYX setup time

3

-

ns

(

8

)

TRDYX hold time

3

-

ns

(9)

Data setup time

3

-

ns

(10)

Data hold time

3

-

ns