205

CHAPTER 10 WATCHDOG TIMER

10.4 Watchdog Timer Operation

The watchdog timer generates a watchdog reset for an overflow of the watchdog

counter.

■

Operation of watchdog timer

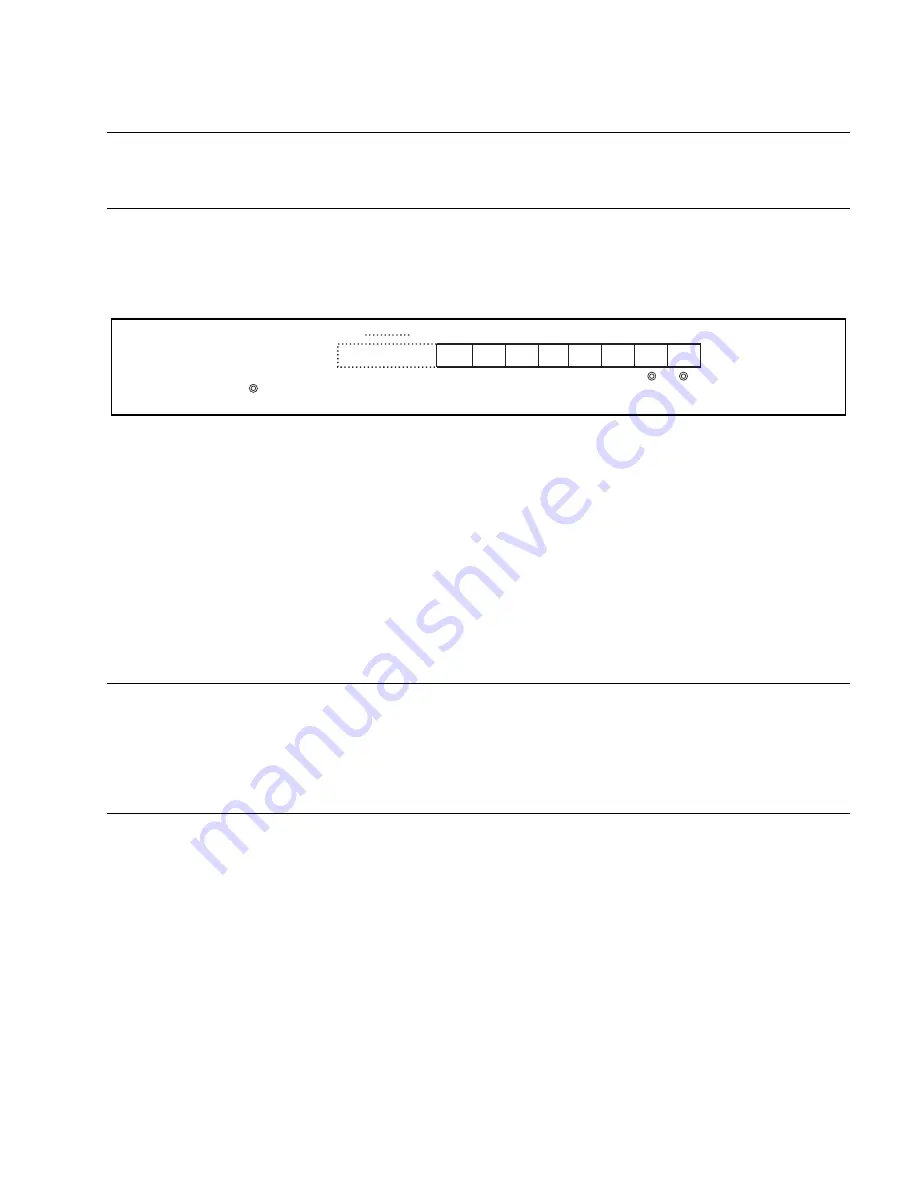

Figure 10.4-1 shows the settings required for operation of the watchdog timer.

Figure 10.4-1 Watchdog timer settings

❍

Starting the watchdog timer

After a reset, the watchdog timer starts operation when the first "0" is written to the watchdog

control bit (WTE) in the watchdog timer control register (WDTC). The interval time is then

specified at the same time on the interval time selection bits (WT1, WT0) in the WDTC register.

❍

Clearing of the watchdog timer

The 2-bit counter of the watchdog timer is cleared when the second or subsequent "0" is written

to the WTE bit. If the counter is not cleared within the interval time, the counter overflows to

generate a watchdog reset.

The watchdog counter is cleared when a reset occurs and by a transition to the sleep mode,

stop mode, timebase timer mode, or clock mode.

Notes:

• When a transition to the timebase timer mode or watch mode occurs, the watchdog counter is

cleared once, but be careful because the watchdog counter does not stop after being cleared.

• When the clock timer is set as watchdog's clock with single clock products, the watchdog timer

cannot be used.

❍

Interval time of the watchdog timer

Figure 10.4-2 shows the relationship between the clear timing and interval time of the watchdog

timer. The interval time varies depending on the timing when the watchdog timer is cleared,

which takes 3.5 to 4.5 times as much time as the count clock cycle.

❍

Check of reset causes

After a reset, the reset cause can be found by checking the reset cause bits (PONR, WRST,

ERST, and SRST) in the WDTC register.

Address

bit15

bit7

bit8

bit6

bit5

bit4

bit3

bit2

bit1

bit0

0000A8

H

WDTC

(TBTC)

PONR

WRST ERST SRST WTE WT1

WT0

0

: Bits being used

0 : Set to "0"

Re-

served

Summary of Contents for MB90480 Series

Page 2: ......

Page 4: ......

Page 10: ...vi ...

Page 128: ...106 CHAPTER 4 RESET ...

Page 174: ...152 CHAPTER 6 LOW POWER CONSUMPTION MODE ...

Page 198: ...176 CHAPTER 7 MODE SETTING ...

Page 220: ...198 CHAPTER 9 TIMEBASE TIMER ...

Page 238: ...216 CHAPTER 11 WATCH TIMER ...

Page 280: ...258 CHAPTER 12 16 BIT INPUT OUTPUT TIMER ...

Page 406: ...384 CHAPTER 17 8 10 BIT A D CONVERTER ...

Page 478: ...456 CHAPTER 20 CHIP SELECTION FACILITY ...

Page 494: ...472 CHAPTER 21 ADDRESS MATCH DETECTION FUNCTION ...

Page 498: ...476 CHAPTER 22 ROM MIRROR FUNCTION SELECTION MODULE ...

Page 526: ...504 CHAPTER 23 2M 3M BIT FLASH MEMORY ...

Page 536: ...514 CHAPTER 24 EXAMPLES OF MB90F481B MB90F482B MB90F488B MB90F489B SERIAL PROGRAMMING ...

Page 570: ...548 CHAPTER 25 PWC TIMER ONLY MB90485 SERIES ...

Page 688: ......