261

CHAPTER 13 8/16-BIT UP/DOWN COUNTER/TIMER

13.2

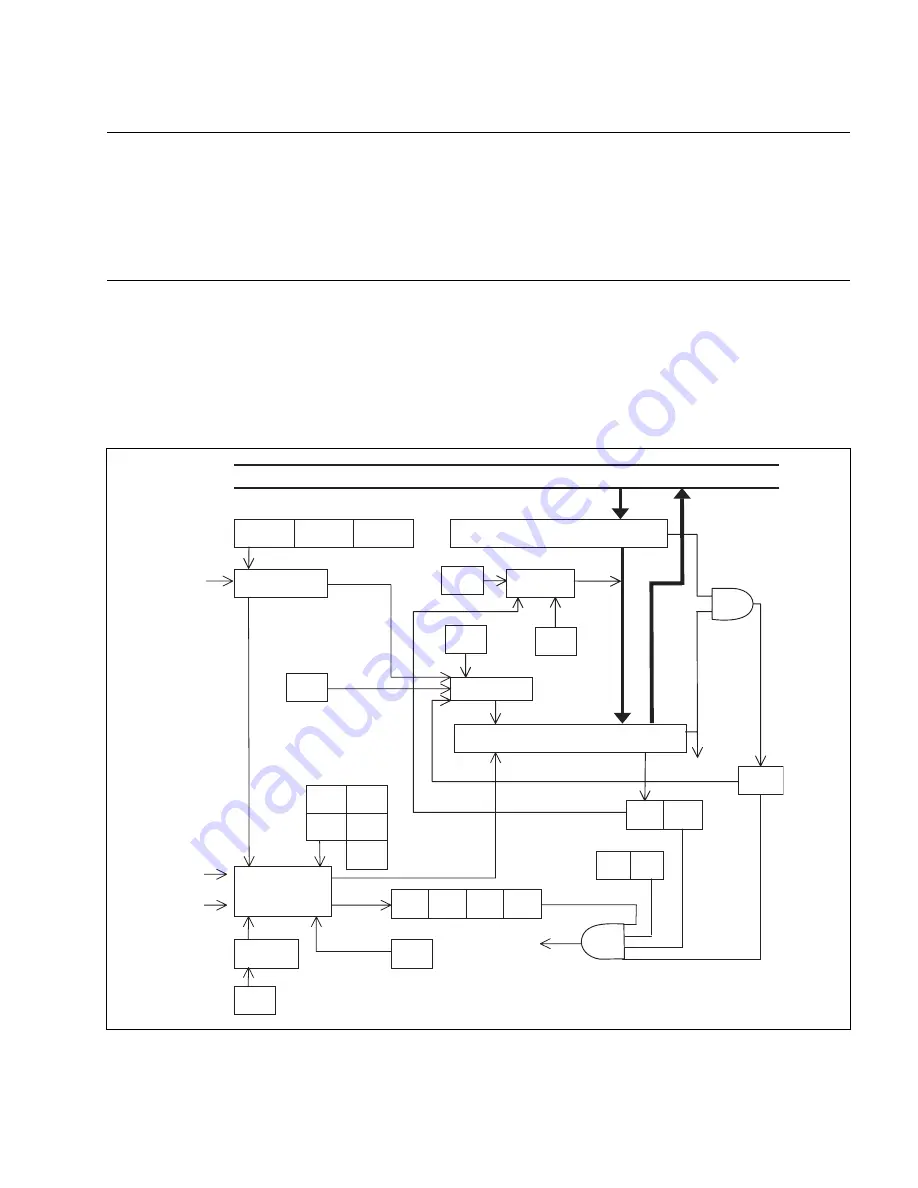

Configuration of 8/16-bit Up/Down Counter/Timer

The 8-bit up/down counter/timer has two channels and consists of three event input

pins, one 8-bit up/down count, and one 8-bit reload/compare register per channel.

Also, one of two 8-bit up/down counter/timer channels can be used as the 16-bit up/

down counter/timer. (When using as the 16-bit up/down counter/timer, the register of

ch.0 is valid.)

■

Block diagram of 8/16-bit up/down counter/timer

Figure 13.2-1 and Figure 13.2-2 are block diagrams of the 8/16-bit up/down counter/timer.

Figure 13.2-1 Block diagram of 8/16-bit up/down counter/timer (channel 0)

Data bus

CGE1

CGE0

CGSC

8 bits

8 bits

RCR0 (reload/compare register 0)

ZIN0

UDCC

Edge/level

detected

CTUT

Reload

control

UCRE

RLDE

Counter clear

UDCR0 (up/down count register 0)

Carry

CMPF

CMS1 CMS0

CES1 CES0

UDMS

AIN0

BIN0

Up/down count

clock selection

UDF1 UDF0 CDCF CFIE

CITE UDIE

Count clock

Interrupt

output

CSTR

CLKS

Prescaler

UDFF OVFF

Summary of Contents for MB90480 Series

Page 2: ......

Page 4: ......

Page 10: ...vi ...

Page 128: ...106 CHAPTER 4 RESET ...

Page 174: ...152 CHAPTER 6 LOW POWER CONSUMPTION MODE ...

Page 198: ...176 CHAPTER 7 MODE SETTING ...

Page 220: ...198 CHAPTER 9 TIMEBASE TIMER ...

Page 238: ...216 CHAPTER 11 WATCH TIMER ...

Page 280: ...258 CHAPTER 12 16 BIT INPUT OUTPUT TIMER ...

Page 406: ...384 CHAPTER 17 8 10 BIT A D CONVERTER ...

Page 478: ...456 CHAPTER 20 CHIP SELECTION FACILITY ...

Page 494: ...472 CHAPTER 21 ADDRESS MATCH DETECTION FUNCTION ...

Page 498: ...476 CHAPTER 22 ROM MIRROR FUNCTION SELECTION MODULE ...

Page 526: ...504 CHAPTER 23 2M 3M BIT FLASH MEMORY ...

Page 536: ...514 CHAPTER 24 EXAMPLES OF MB90F481B MB90F482B MB90F488B MB90F489B SERIAL PROGRAMMING ...

Page 570: ...548 CHAPTER 25 PWC TIMER ONLY MB90485 SERIES ...

Page 688: ......