285

CHAPTER 13 8/16-BIT UP/DOWN COUNTER/TIMER

13.6

Program Example of 8/16-bit Up/Down Counter/Timer

This section describes the program example of the 8/16-bit up/down counter/timer.

■

Program example of 8/16-bit up/down counter/timer

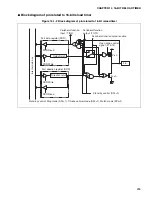

Example of setting procedure

16-bit mode timer mode (down count) Count clock = 8

division

Reload count value and generate interval

interrupt. Interrupt source = underflow

Program example

void UD0_sample_1(void)

{

UD0_initial();

UD0_start();

}

<Initial setting>

•

Control up/down counter ch.0

•

Set reload value/compare value

•

Interrupt related

void UD0_initial(void)

{

IO_CCR0.word = 0x9018;/*Setting value=1001_0000_0001_1000 */

/* bit15 = 1

M16E 16bit

×

1ch operation mode */

/* bit14 = 0

Clear CDCF count direction reversal flag */

/* bit13 = 0

Disable CFIE direction reversal interrupt

*/

/* bit12 = 1

CLKS 8 machine cycles */

/* bit11-10 = 00 CMS1, 0 timer mode */

/* bit9-8 = 00

Disable CES1, 0 edge detection */

/* bit7 = 0

Select UMDS up/down mode */

/* bit6 = 0

Write CTUT counter (invalid) */

/* bit5 = 0

Disable UCRE counter clear */

/* bit4 = 1

Enable RLDE reload function */

/* bit3 = 1

Clear UDCC UDCR (invalid) */

/* bit2 = 0

CGSC ZIN counter clear function */

/* bit1-0 = 00

Disable CGE1, 0 ZIN edge detection

*/

IO_RCR0 = 0xff;

/* Set 16-bit mode reload value (arbitrary value) */

IO_RCR1 = 0xff;

IO_ICR07.byte = 0x10;

/* Set interrupt level (arbitrary value) */

__EI();

/*Enable interrupt */

}

<Start>

•

Start up/down counter ch.0

void UD0_start(void)

{

IO_CSR0.bit.UDIE = 1;

/* bit5 = 1

Enable UDIE underflow interrupt */

IO_CCR0.bit.CTUT = 1;

/* bit6 = 1

Write CTUT counter */

IO_CSR0.bit.CSTR = 1;

/* bit7 = 1

Activate CSTR count operation */

}

<Interrupt>

•

Interrupt processing

__interrupt void UD0_int(void)

{

if(IO_CSR0.bit.UDFF)

{

IO_CSR0.bit.UDFF = 0;

/* bit2 = 0

Clear UDFF underflow detection flag */

•••••

}

}

<Interrupt vector>

•

Set vector table

#pragma intvect UD0_int 25

Note:

Setting related to clock and setting of _set_il (numeric

value) are required in advance. See the chapter of

clock and interrupt.

Note:

For the description form of the register, see "SAMPLE I/O REGISTER FILES FOR

F

2

MC-16LX FAMILY MB90480 SERIES".

Set control register

CCR0

Set 16-bit mode enable>>

.M16E

Reverse count direction>>

.CDCF

Enable count direction reversal interrupt>>

.CFIE

Select built-in prescaler>>

.CLKS

Select count mode>>

.CMS1-0

Select count clock edge>>

.CES1-0

Select up/down mode>>

.UDMS

Write counter>>

.CTUT

Enable UDCR clear>>

.UCRE

Enable reload function>>

.RLDE

UDCR clear>>

.UDCC

Counter clear/gate selection>>

.CGSC

Counter clear/gate edge selection

>>

.CGE1-0

Set reload value

RCR0

RCR1

Set UD counter 0 interrupt level

ICR07

Set I flag

(CCR)

Register name. bit name

Control underflow interrupt

CSR0 .UDIE

Transfer data from RCR to

UDCR

CCR0 .CTUT

Start count operation

CSR0 .CSTR

Check underflow detection flag

Clear interrupt request flag

CSR0 .UDFF

(Arbitrary processing)

Summary of Contents for MB90480 Series

Page 2: ......

Page 4: ......

Page 10: ...vi ...

Page 128: ...106 CHAPTER 4 RESET ...

Page 174: ...152 CHAPTER 6 LOW POWER CONSUMPTION MODE ...

Page 198: ...176 CHAPTER 7 MODE SETTING ...

Page 220: ...198 CHAPTER 9 TIMEBASE TIMER ...

Page 238: ...216 CHAPTER 11 WATCH TIMER ...

Page 280: ...258 CHAPTER 12 16 BIT INPUT OUTPUT TIMER ...

Page 406: ...384 CHAPTER 17 8 10 BIT A D CONVERTER ...

Page 478: ...456 CHAPTER 20 CHIP SELECTION FACILITY ...

Page 494: ...472 CHAPTER 21 ADDRESS MATCH DETECTION FUNCTION ...

Page 498: ...476 CHAPTER 22 ROM MIRROR FUNCTION SELECTION MODULE ...

Page 526: ...504 CHAPTER 23 2M 3M BIT FLASH MEMORY ...

Page 536: ...514 CHAPTER 24 EXAMPLES OF MB90F481B MB90F482B MB90F488B MB90F489B SERIAL PROGRAMMING ...

Page 570: ...548 CHAPTER 25 PWC TIMER ONLY MB90485 SERIES ...

Page 688: ......