331

CHAPTER 15 8/16-BIT PPG TIMER

15.4

Interrupt of 8/16-Bit PPG Timer

The interrupt of the 8/16-bit PPG timer occurs when the PPG counter underflow is

detected.

The interrupt of the PPG counter underflow cannot activate the DMA transfer and

extended intelligent I/O service (EI

2

OS).

■

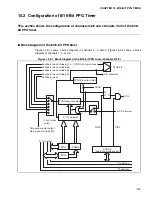

Interrupt of 8/16-bit PPG timer

Table 15.4-1 shows the interrupt control bit and interrupt source of the 8/16-bit PPG timer.

■

Interrupt of PPG counter underflow

●

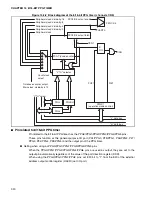

8-bit PPG and 8 + 8-bit PPG output operation mode

•

In the 8-bit PPG 6-channel independent operation mode or the 8 + 8-bit PPG output

operation mode, the interrupt can be generated independently.

•

When the value of the PPG down counter is decremented from "00

H

" to "FF

H

", an underflow

occurs. When an underflow occurs, the underflow bit in the channel causing an underflow is

set (PUF0 = 1, PUF1 = 1).

●

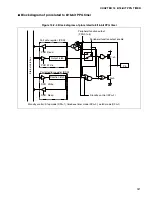

16-bit PPG output operation mode

•

In the 16-bit PPG output operation mode, when the values of the PPG0 + PPG1/PPG2 +

PPG3/PPG4 + PPG5 down counters are decremented from "0000

H

" to "FFFF

H

", an underflow

occurs. When an underflow occurs, the underflow generation bits in the two channels are set

at one time (PIF0 = 1, PIF1 = 1).

•

When an underflow occurs with either of the two channels of the interrupt requests enabled

(PIE0 = 0 + PIE1 = 1, PIE0 = 1 + PIE1 = 0), an interrupt is generated.

•

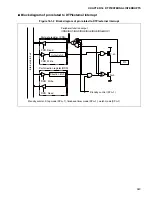

To prevent duplication of interrupt requests, disable either of the two channels of the

underflow interrupt enable bits (PIE0 = 0 + PIE1 = 1, PIE0 = 1 + PIE1 = 0).

•

When the two channels of the underflow generation flag bits are set (PUF0 = 1, PUF1 = 1),

clear the two channels at the same time.

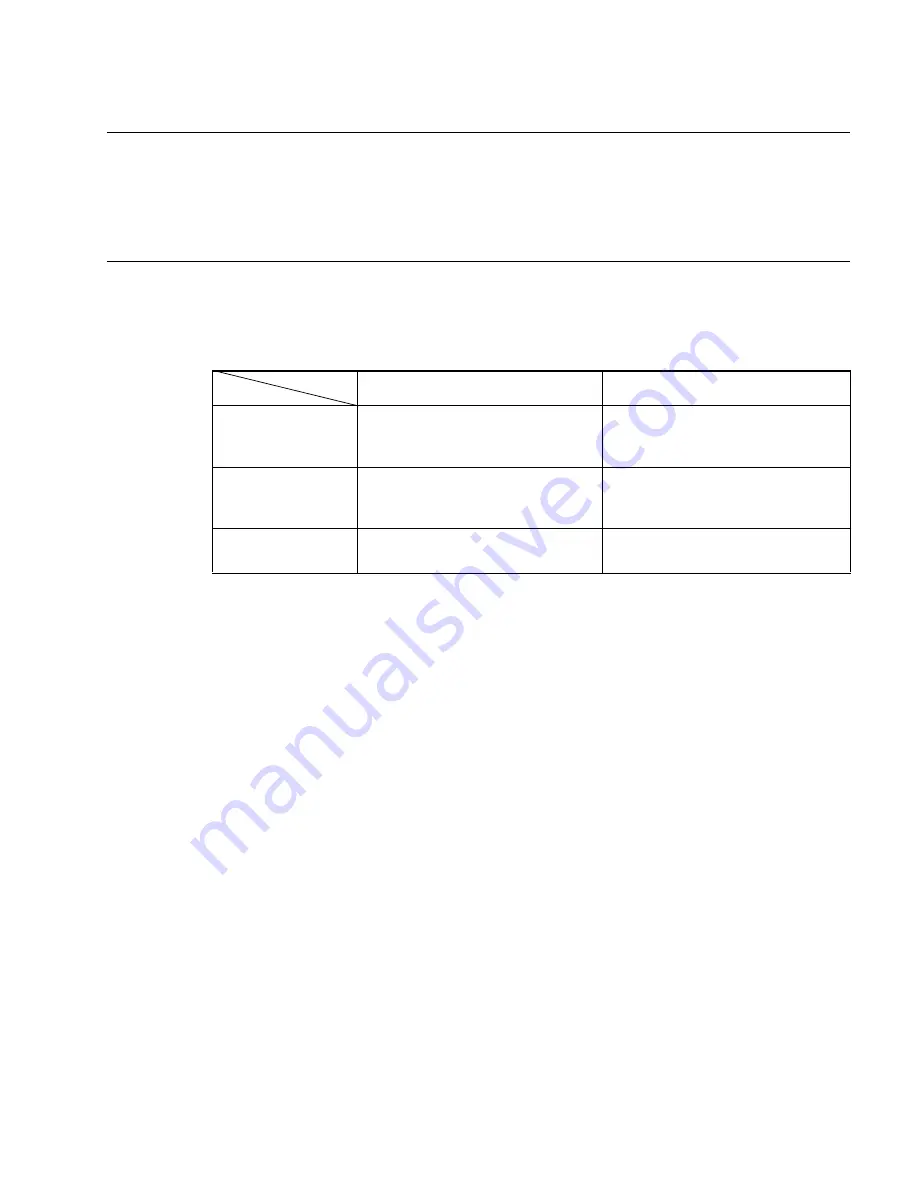

Table 15.4-1 Interrupt of 8/16-bit input/output timer

PPG0/2/4 overflow interrupt

PPG1/3/5 overflow interrupt

Interrupt request flag

PPG0:PUF0 (bit3) ch.0

PPG2:PUF0 (bit3) ch.2

PPG4:PUF0 (bit3) ch.4

PPG1:PUF1 (bit3) ch.1

PPG3:PUF1 (bit3) ch.3

PPG5:PUF1 (bit3) ch.5

Interrupt request

output enable bit

PPG0:PUE0 (bit4) ch.0

PPG2:PUE0 (bit4) ch.2

PPG4:PUE0 (bit4) ch.4

PPG1:PUE1 (bit4) ch.1

PPG3:PUE1 (bit4) ch.3

PPG5:PUE1 (bit4) ch.5

Interrupt generation

source

Overflow in PPG0/PPG2/PPG4 down

counter

Overflow in PPG1/PPG3/PPG5 down

counter

Summary of Contents for MB90480 Series

Page 2: ......

Page 4: ......

Page 10: ...vi ...

Page 128: ...106 CHAPTER 4 RESET ...

Page 174: ...152 CHAPTER 6 LOW POWER CONSUMPTION MODE ...

Page 198: ...176 CHAPTER 7 MODE SETTING ...

Page 220: ...198 CHAPTER 9 TIMEBASE TIMER ...

Page 238: ...216 CHAPTER 11 WATCH TIMER ...

Page 280: ...258 CHAPTER 12 16 BIT INPUT OUTPUT TIMER ...

Page 406: ...384 CHAPTER 17 8 10 BIT A D CONVERTER ...

Page 478: ...456 CHAPTER 20 CHIP SELECTION FACILITY ...

Page 494: ...472 CHAPTER 21 ADDRESS MATCH DETECTION FUNCTION ...

Page 498: ...476 CHAPTER 22 ROM MIRROR FUNCTION SELECTION MODULE ...

Page 526: ...504 CHAPTER 23 2M 3M BIT FLASH MEMORY ...

Page 536: ...514 CHAPTER 24 EXAMPLES OF MB90F481B MB90F482B MB90F488B MB90F489B SERIAL PROGRAMMING ...

Page 570: ...548 CHAPTER 25 PWC TIMER ONLY MB90485 SERIES ...

Page 688: ......