GENERAL

1-13

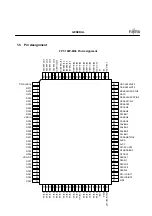

1.8

Notes on Handling Devices

(1) Be careful not to exceed the maximum rated voltage (Prevention of latch up).

For a CMOS IC, latch-up may occur if a voltage higher than Vcc or a voltage lower than Vss is applied to the

I/O pin other than medium-/high-voltage withstand I/O pins, or when a voltage that exceeds the rated

voltage is applied between Vcc and Vss.

Latch up rapidly increases the power current, and the device may be destroyed by heat.

When using the device, take care not to exceed the maximum rating. Also, take care that the analog power

(AVcc) and the analog input do not exceed the digital power (Vcc) when turning the AC/DC power on or off.

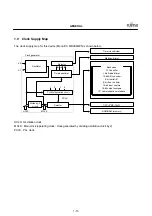

(2) Design the device so the supply voltage is as stable as possible.

A sudden change in the power voltage may cause a malfunction even within the operating assurance range

of the VCC power supply voltage. For safety, the VCC ripple (p-p) of the commercial frequency (50/60

MHz) must be 10% or less of the standard VCC value, and the transient fluctuation at instantaneous power

switching must be 0.1 V/ms or less. Also, take countermeasures to power noise, etc.

(3) Notes at power-on

The voltage rise time at power-on must be 50 µs or more (0.2 to 2.7 V).

(4) Setting unused input pins

Leaving unused input pins open may cause a malfunction. Therefore, these pins must be set to the pull-

up or pull-down state.

(5) Handling of power pins for A/D converter

Even when the A/D converter is not used, connect the pins so that the following relationships are

established: AV

CC

= V

CC

, AV

SS

= V

SS

.

(6) Notes on using external clock

Even when an external clock is used, the oscillation stabilization wait time is required at the power-on reset

or the cancellation of the stop mode. In this case, drive the X0 pin only and leave the X1 pin open.

Example of using external clock

X0

X1

MB90M405 Series

OPEN

Summary of Contents for MB90M405

Page 2: ...ii ...

Page 6: ...MB90M405 F2 MC 16LX FAMILY HARDWARE MANUAL 1 2 ...