MB91401

42

(Continued)

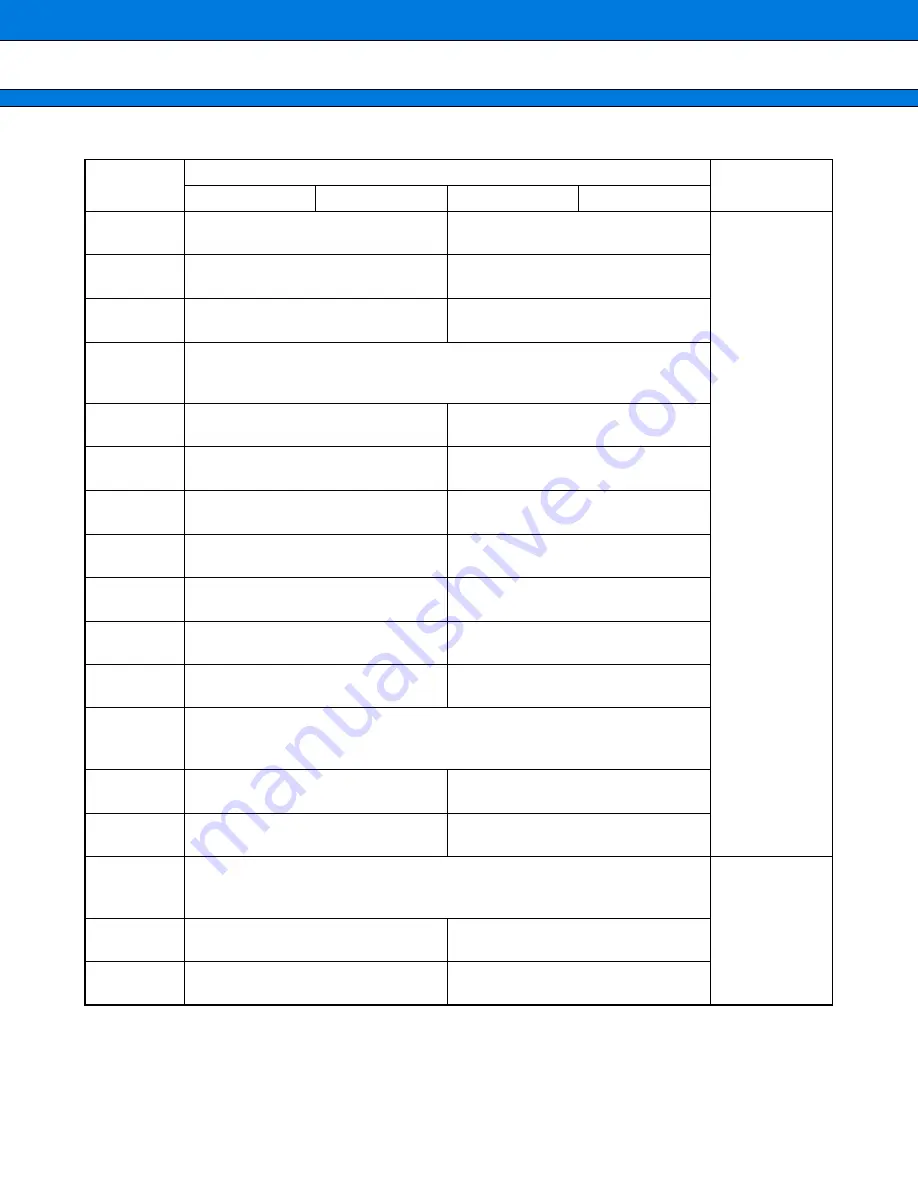

Address

Register

Block

++++

0

++++

1

++++

2

++++

3

0540_0000

H

FIFO0out[R]

XXXXXXXX-XXXXXXXX

FIFO0in[W]

XXXXXXXX-XXXXXXXX

USB

0540_0004

H

FIFO1[R]

XXXXXXXX-XXXXXXXX

FIFO2[W]

XXXXXXXX-XXXXXXXX

0540_0008

H

FIFO3[W]

XXXXXXXX-XXXXXXXX

0540_000C

H

to

0540_001F

H

(Reserved)

0540_0020

H

CONT1[R/W]

XXXXX0XX-XXX00000

0540_0024

H

CONT2[R/W]

XXXXXXXX_XXX00000

CONT3[R/W]

XXXXXXXX_XXX00000

0540_0028

H

CONT4[R/W]

XXXXXXXX_XXX00000

CONT5[R/W]

XXXXXXXX_XXXX00XX

0540_002C

H

CONT6[R/W]

XXXXXXXX_XXXX00XX

CONT7[R/W]

XXXXXXXX_XXX00000

0540_0030

H

CONT8[R/W]

XXXXXXXX_XXX00000

CONT9[R/W]

XXXXXXXX_0XXX0000

0540_0034

H

CONT10[R/W]

XXXX0000_X000000X

TTSIZE[R/W]

00010001-00010001

0540_0038

H

TRSIZE[R/W]

00010001-00010001

0540_003C

H

to

0540_003F

H

(Reserved)

0540_0040

H

RSIZE0[R]

XXXXXXXX-XXXX0000

0540_0044

H

RSIZE1[R]

XXXXXXXX-X0000000

0540_0048

H

to

0540_005F

H

(Reserved)

USB

0540_0060

H

ST1[R/W]

XXXXXX00-00000000

0540_0064

H

Summary of Contents for MB91401

Page 71: ...MB91401 71 MEMO ...