MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

117

CHAPTER 9 WATCH PRESCALER

9.4 Operations and Setting Procedure

Example

•

In sub-CR clock mode

Only the sub-CR clock is used as the input clock of the watch prescaler.

■

Operation Example of Watch Prescaler

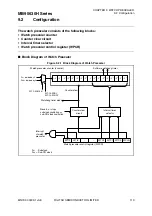

Figure 9.4-1 shows an operation example under the following conditions:

1. When a power-on reset occurs

2. When the device transits to the sleep mode during the operation of the interval timer

function in subclock mode or sub-CR clock mode

3. When the device transits to the stop mode during the operation of the interval timer

function in subclock mode or sub-CR clock mode

4. When a request for clearing the counter is issued

The same operation is performed when changing to the watch mode as for when changing to

the sleep mode.

Figure 9.4-1 Watch Prescaler Operation Example

WTIF

b

it

WTIE

b

it

2)

S

LP

b

it

(

S

TBC regi

s

ter)

3

)

S

TP

b

it

(

S

TBC regi

s

ter)

Co

u

nter v

a

l

u

e

(co

u

nt down)

0x0000

O

s

cill

a

tion

s

t

ab

iliz

a

tion w

a

it time

1) Power-on re

s

et

Interv

a

l time

(WPCR:WTC[2:0] = 0

b

011)

0xFFFF

S

leep

S

top

S

leep mode

rele

as

ed

b

y w

a

tch interr

u

pt

S

top mode rele

as

ed

b

y extern

a

l interr

u

pt

• When

s

etting interv

a

l time

s

elect

b

it

s

in the w

a

tch pre

s

c

a

ler control regi

s

ter (WPCR:WTC[2:0]) to "0

b

011" (2

14

×

2/F

CL

)

Co

u

nt v

a

l

u

e detected in

WPCR:WTC[2:0]

4)

• WPCR:WTC[2:0]

• WPCR:WCLR

• WPCR:WTIF

• WPCR:WTIE

•

S

TBC:

S

LP

•

S

TBC:

S

TP

: W

a

tch pre

s

c

a

ler interr

u

pt interv

a

l time

s

elect

b

it

s

in w

a

tch pre

s

c

a

ler control regi

s

ter

: W

a

tch pre

s

c

a

ler cle

a

r

b

it in w

a

tch pre

s

c

a

ler control regi

s

ter

: W

a

tch pre

s

c

a

ler interr

u

pt re

qu

e

s

t fl

a

g

b

it in w

a

tch pre

s

c

a

ler control regi

s

ter

: W

a

tch pre

s

c

a

ler interr

u

pt re

qu

e

s

t en

ab

le

b

it in w

a

tch pre

s

c

a

ler control regi

s

ter

:

S

leep

b

it in

s

t

a

nd

b

y control regi

s

ter

:

S

top

b

it in

s

t

a

nd

b

y control regi

s

ter

Co

u

nter cle

a

red

(WPCR:WCLR = 1)

Cle

a

red

a

t interv

a

l

s

etting

Cle

a

red in interr

u

pt

proce

ss

ing ro

u

tine

Cle

a

red

b

y tr

a

n

s

ition

to

s

top mode

O

s

cill

a

tion

s

t

ab

iliz

a

tion

w

a

it time