MB95630H Series

144

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 11 8/16-BIT COMPOSITE TIMER

11.6 Operation of Interval Timer Function

(One-shot Mode)

11.6

Operation of Interval Timer Function (One-shot

Mode)

This section describes the operation of the interval timer function (one-shot

mode) of the 8/16-bit composite timer.

■

Operation of Interval Timer Function (One-shot Mode)

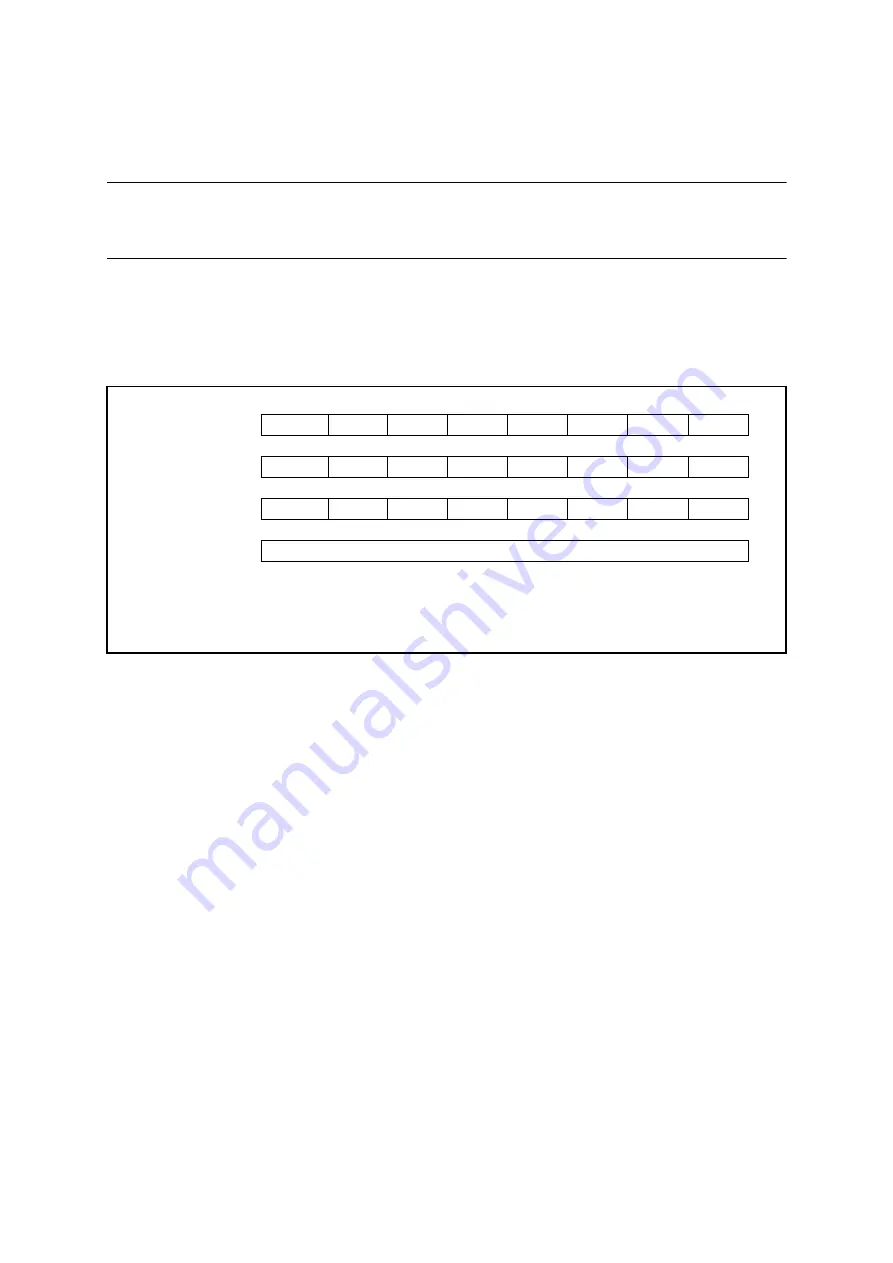

The register settings shown in Figure 11.6-1 are required to use the interval timer function

(one-shot mode).

Figure 11.6-1 Settings of Interval Timer Function (One-shot Mode)

As for the interval timer function (one-shot mode), enabling timer operation (Tn0CR1/

Tn1CR1:STA = 1) causes the counter to start counting from "0x00" at the rising edge of a

selected count clock signal. When the counter value matches the value of the 8/16-bit

composite timer data register (Tn0DR/Tn1DR), the timer output (TMCRn:TO0/TO1) is

inverted, the interrupt flag (Tn0CR1/Tn1CR1:IF) is set to "1", the timer operation enable bit

(Tn0CR1/Tn1CR1:STA) is set to "0", and the counter stops counting.

The value of the 8/16-bit composite timer data register (Tn0DR/Tn1DR) is transferred to the

temporary storage latch (comparison data storage latch) in the comparator when the counter

starts counting. Do not write "0x00" to the 8/16-bit composite timer data register.

Figure 11.6-2 shows the operation of the interval timer function in 8-bit operation.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Tn0CR0/Tn1CR0

IFE

C2

C1

C0

F3

F2

F1

F0

❍

❍

❍

❍

0

0

0

0

Tn0CR1/Tn1CR1

STA

HO

IE

IR

BF

IF

SO

OE

1

❍

❍

×

×

❍

❍

❍

TMCRn

TO1

TO0

TIS

MOD

FE11

FE10

FE01

FE00

❍

❍

×

❍

❍

❍

❍

❍

Tn0DR/Tn1DR

Sets interval time (counter compare value)

❍

: Used bit

×: Unused bit

1: Set to "1"

0: Set to "0"