MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

153

CHAPTER 11 8/16-BIT COMPOSITE TIMER

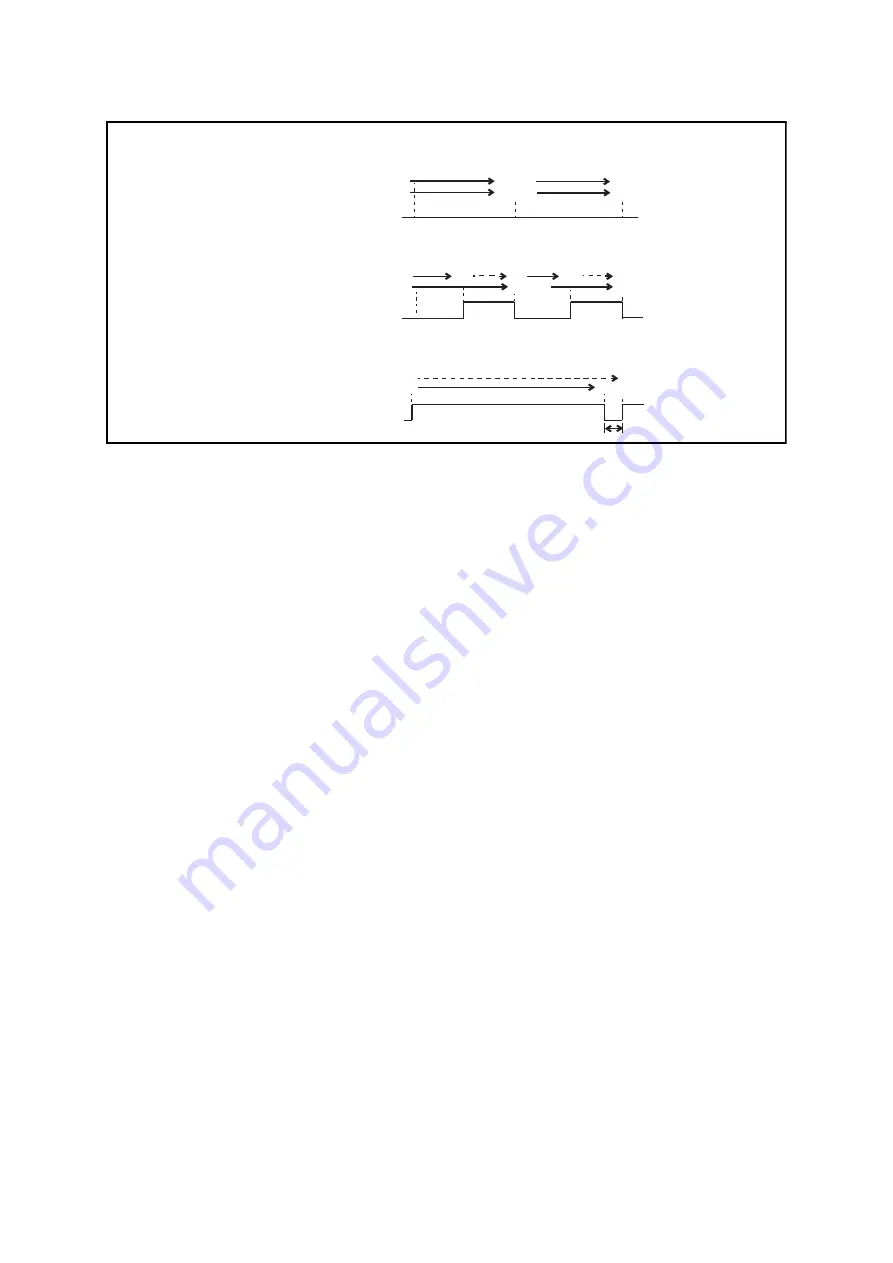

11.10 Operation of PWM Timer Function

(Variable-cycle Mode)

Figure 11.10-2 Operation Diagram of PWM Timer Function (Variable-cycle Mode)

Co

u

nter timer n0 v

a

l

u

e

"H"

"L"

"H"

"L"

"H"

"L"

0x00

PWM w

a

veform

PWM w

a

veform

PWM w

a

veform

Tn0DR regi

s

ter v

a

l

u

e: "0x

8

0", Tn1DR regi

s

ter v

a

l

u

e: "0x

8

0" (d

u

ty r

a

tio = 0%)

0xFF, 0x00

0x

8

0, 0x00

0x00

0x

8

0, 0x00

0x

8

0, 0x00

0x00

0x

8

0, 0x00

Co

u

nter timer n1 v

a

l

u

e

Co

u

nter timer n0 v

a

l

u

e

Co

u

nter timer n1 v

a

l

u

e

0x00

0x00

0x00

0x

8

0, 0x00

0x00

0x

8

0, 0x00

0x40

0x40

Co

u

nter timer n0 v

a

l

u

e

Co

u

nter timer n1 v

a

l

u

e

0x00

0x00

One co

u

nt width

(timer n0 v

a

l

u

e

≥

timer n1 v

a

l

u

e)

Tn0DR regi

s

ter v

a

l

u

e: "0x40", Tn1DR regi

s

ter v

a

l

u

e: "0x

8

0" (d

u

ty r

a

tio = 50%)

Tn0DR regi

s

ter v

a

l

u

e: 0x00", Tn1DR regi

s

ter v

a

l

u

e: "0xFF" (d

u

ty r

a

tio = 99.6%)