MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

209

CHAPTER 14 LIN-UART

14.4 Interrupts

14.4.1

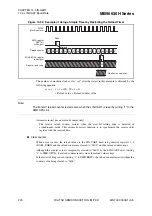

Timing of Receive Interrupt Generation and Flag

Set

A receive interrupt is generated when reception is completed (SSR:RDRF) or

when a reception error occurs (SSR:PE, ORE, FRE).

■

Timing of Receive Interrupt Generation and Flag Set

Received data is stored in the LIN-UART receive data register (RDR) when the first stop bit is

detected in operating mode 0/1/2(SSM = 1)/3, or when the last data bit is detected in operating

mode 2 (SSM = 0). When reception is completed (SSR:RDRF = 1), or when a reception error

occurs (SSR:PE, ORE, FRE = 1), an error flag corresponding to one of the events mentioned above

is set. If the receive interrupt has been enabled (SSR:RIE = 1) when an error flag is set, a receive

interrupt is generated.

Note:

In all operating modes, when a receive error occurs, data in the LIN-UART receive data

register (RDR) becomes invalid.

Figure 14.4-2 shows the timing of reception and flag set.

Figure 14.4-2 Timing of Reception and Flag Set

Note:

Figure 14.4-2 does not show all reception operations in mode 0. It only shows two

examples of reception operations using different communication formats. One reception

operation uses 7-bit data, a parity bit (parity bit = "even parity" or "odd parity") and one

stop bit. The other uses 8-bit data, no parity bit and one stop bit.

RDRF

PE

*1

, FRE

ORE

*2

(RDRF = 1)

S

T

D0

D1

D2

D5

D6

D7/P

S

P

S

T

S

T

D0

D1

D2

D6

D7

AD

S

P

S

T

D0

D1

D2

...

...

...

D4

D5

D6

D7

D0

Received data

(Operating mode 0/3)

Received data

(Operating mode 1)

Received data

(Operating mode 2)

Receive interrupts generated

*

1: The PE flag is always "0" in operating mode 1 and operating mode 3.

*

2: An overrun error occurs if the next data is transferred before received data is read (RDRF = 1).

ST: Start bit, SP: Stop bit, AD: Operating mode 1 (multiprocessor) address data select bit