MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

293

CHAPTER 17 CLOCK SUPERVISOR COUNTER

17.3 Operations

17.3

Operations

This section describes the operations of the clock supervisor counter.

■

Clock Supervisor Counter

●

Clock Supervisor Counter Operation 1

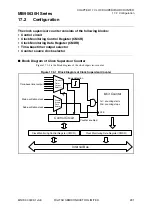

The clock supervisor counter is first enabled by the software (CMCEN = 1), and then the clock

supervisor counter operates with the time-base timer interval selected from eight options by the

TBTSEL[2:0] bits. Between two rising edges of the time-base timer interval selected, the

internal counter is clocked by the external clock.

The count clock of this module can be selected from the main oscillation clock and the sub-

oscillation clock.

Figure 17.3-1 Clock Supervisor Counter Operation 1

●

Clock Supervisor Counter Operation 2

The CMDR register is cleared when the CMCEN bit changes from "0" to "1".

Figure 17.3-2 Clock Supervisor Counter Operation 2

S

elected time-

bas

e

timer interv

a

l

M

a

in/

Sub

-o

s

cill

a

tion clock

CMCEN

Intern

a

l co

u

nter

CMDR regi

s

ter

0

0

3

0

3

0

S

elected time-

bas

e

timer interv

a

l

M

a

in/

Sub

-o

s

cill

a

tion clock

CMCEN

Intern

a

l co

u

nter

CMDR regi

s

ter

Cle

a

r

0

0

0

0

10

10

10

10