MB95630H Series

296

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 17 CLOCK SUPERVISOR COUNTER

17.3 Operations

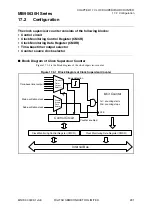

Table 17.3-1 is calculated by the following equation:

If the time-base timer interrupt is used to make the clock supervisor counter wait for the

oscillation stabilization time, please satisfy the following condition:

Time-base Timer Interval > Main/Sub-oscillation Stabilization Time

×

1.05

e.g. F

CH

= 4 MHz, F

CRH

= 1 MHz, MWT[3:0] = 0b1111 (in WATR register)

Time-base Timer Interval >

TBC[3:0] = 0b0110 (2

13

×

1/F

CRH

)

Notes:

•

See "7.1 Overview" for time-base timer interval settings.

•

See "3.3.3 Oscillation Stabilization Wait Time Setting Register (WATR)" for main/

sub-oscillation stabilization time settings.

Co

u

nter v

a

l

u

e =

2

3

×

1/F

CRH

(TBT

S

EL=000)

2

5

×

1/F

CRH

(TBT

S

EL=001)

2

7

×

1/F

CRH

(TBT

S

EL=010)

2

9

×

1/F

CRH

(TBT

S

EL=011)

2

11

×

1/F

CRH

(TBT

S

EL=100)

2

1

3

×

1/F

CRH

(TBT

S

EL=101)

2

15

×

1/F

CRH

(TBT

S

EL=110)

2

17

×

1/F

CRH

(TBT

S

EL=111)

×

M

a

in/

Sub

-O

s

cill

a

tion Clock Fre

qu

ency

2

±

1 (Me

asu

rement error)

*Omit the decim

a

l pl

a

ce

s

of “V

a

l

u

e”.

S

elected time-

bas

e

timer interv

a

l

Within thi

s

period, the “V

a

l

u

e” in the

ab

ove e

qua

tion i

s

co

u

nted

b

y the m

a

in/

sub

o

s

cill

a

tion clock.

2

14

2

)

–

(

4

10

6

×

-----------------------

1.05

4.3ms

≈

×