MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

423

CHAPTER 21 MULTI-PULSE GENERATOR

21.5 Operations

■

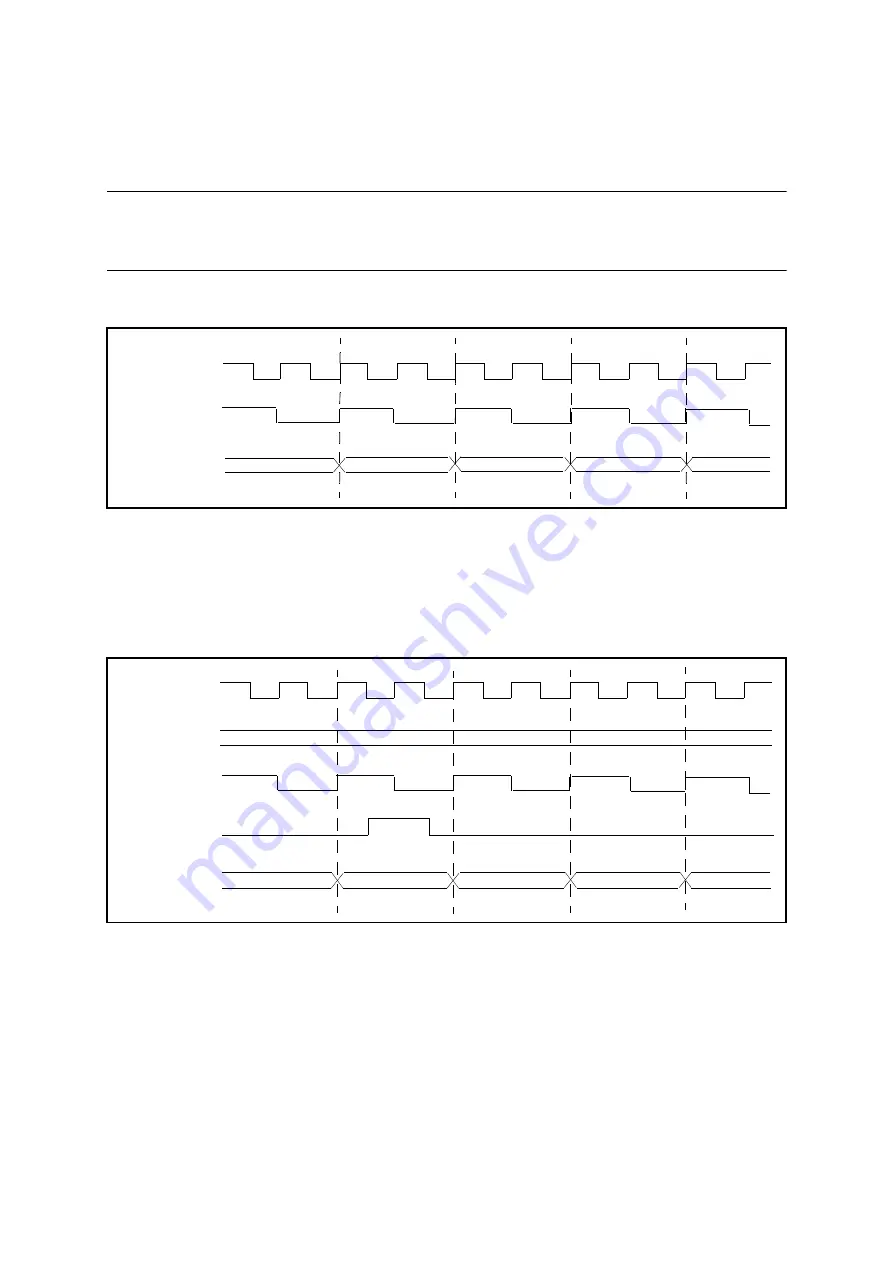

16-bit Timer Timing

The 16-bit timer increases its value at timing according to the prescaler clock and counts up at

a rising edge.

Note:

Before the prescaler clock is changed, the Timer Counter should be disabled first by

setting the TMEN bit to "0".

Figure 21.5-29 16-bit Timer Count Timing

The counter can be cleared upon a reset, software clear (TCLR), a match with the compare

clear register, the Write Timing signal or the Position Detection signal. By a reset, the counter

is immediately cleared. By a match with the compare clear register, software clear (TCLR), the

Write Timing signal or the Position Detection signal, the counter is cleared in synchronization

with the count timing.

Figure 21.5-30 16-bit Timer Clear Timing

N

N+1

Counter value

Prescaler clock

N+2

N+3

N+4

CPU clock

N

N - 1

0x0000

Compare

register value

Compare match

Counter value

Prescaler clock

N

0x0001

0x0002

MCLK