MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

425

CHAPTER 21 MULTI-PULSE GENERATOR

21.5 Operations

■

Using 16-bit Timer of Multi-pulse Generator

The timer is reset when write timing or position detection interrupt flag is set, which is

selectable by the MODE bit in the 16-bit MPG timer control status register (TCSR).

The timer can be started or stopped by setting the TMEN bit in the 16-bit MPG timer control

status register (TCSR). There is no timer overflow interrupt. Whenever the timer is restarted,

the current counter value is latched to a buffer for speed calculation.

If the counter value matches the 16-bit MPG compare clear register (upper/lower) (CPCUR/

CPCLR), it interrupts the CPU and the timer is reset.

Note:

If the values loaded to the 16-bit MPG compare clear register (upper) (CPCUR) and the

16-bit MPG compare clear register (lower) (CPCLR) are the same as the timer counter

value, the comparison operation will not be performed until the next occasion in which the

values of CPCUR and CPCLR are the same as the timer counter value.

The Compare Clear interrupt shares the same interrupt vector with the Write Timing interrupt

while Compare Match interrupt shares the same vector as that of the Position Detect interrupt.

■

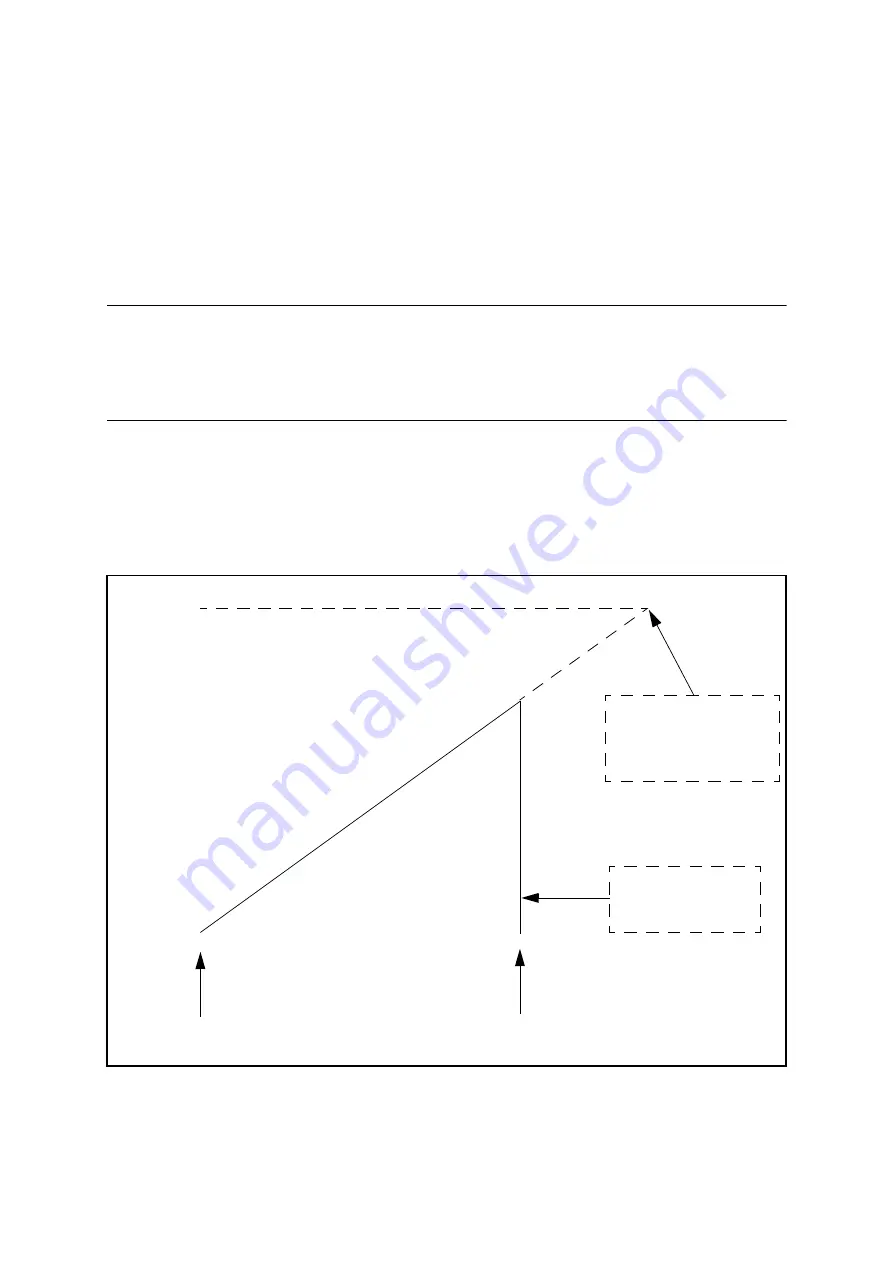

16-bit Timer in Multi-pulse Generator Operation Diagram

Figure 21.5-32 16-bit Timer in Multi-pulse Generator Operation Diagram

Counter value

Compare

Clear

Register

Timer is reset, which is triggered

by write timing or position detection.

Timer is reset, which is triggered

by write timing or position detection.

Current counter

value is latched

into buffer.

If no desired position

detect signal appears

before a timeout period,

it means abnormal.

(CPCUR,

CPCLR)