MB95630H Series

30

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 3 CLOCK CONTROLLER

3.3 Registers

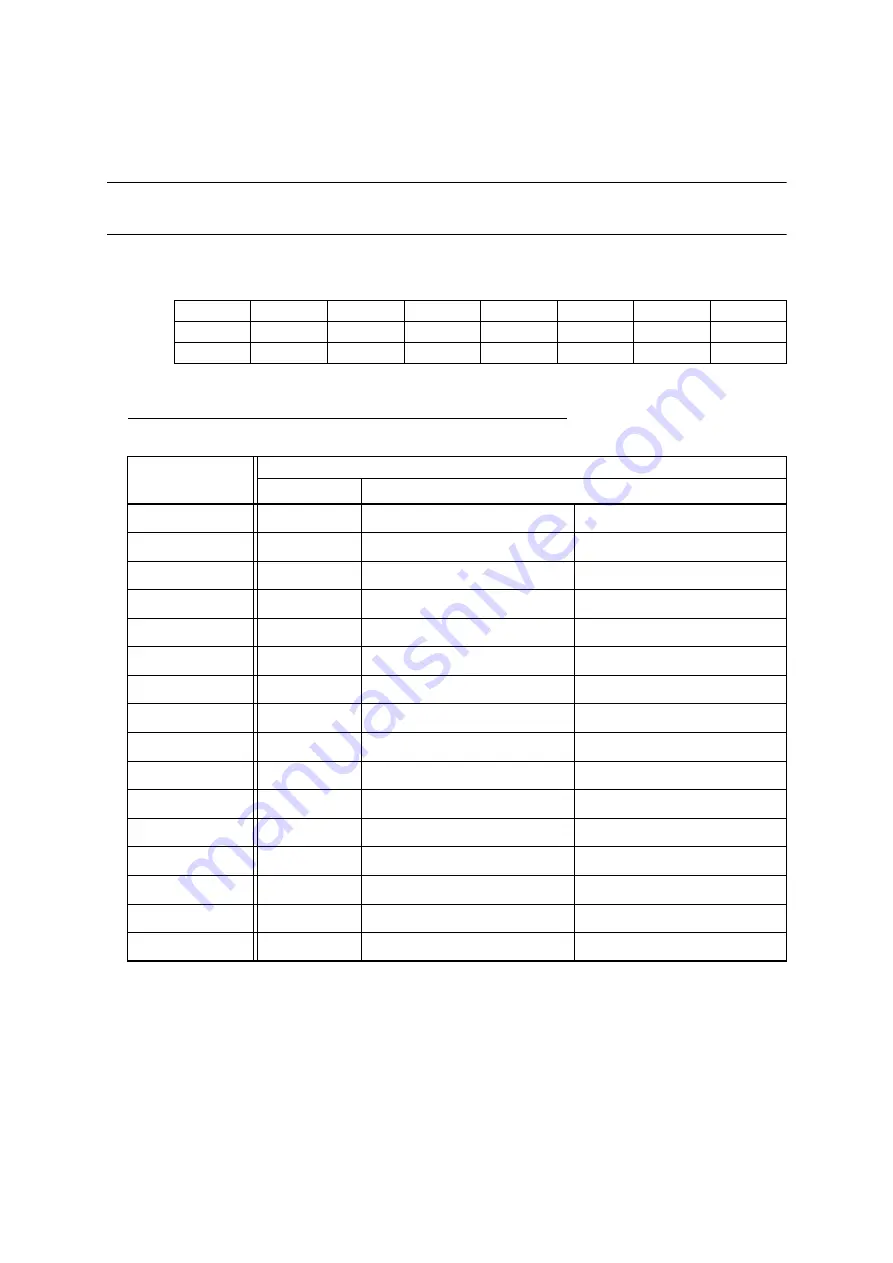

3.3.3

Oscillation Stabilization Wait Time Setting

Register (WATR)

This register selects oscillation stabilization wait times.

■

Register Configuration

■

Register Functions

[bit7:4] SWT[3:0]: Subclock oscillation stabilization wait time select bits

These bits set the subclock oscillation stabilization wait time.

The number of cycles in the above table is the minimum value. The maximum value is the number of cycles

in the above table plus 1/F

CL

.

Note: Do not modify these bits during subclock oscillation stabilization wait time. Modify them when the

subclock oscillation stabilization bit in the system clock control register 2 (SYCC2:SRDY) has been

set to "1". These bits can be modified when the subclock is stopped with the subclock oscillation stop

bit in the system clock control register 2 (SYCC2:SOSCE) set to "0" in main clock mode, main CR

clock mode, main CR PLL clock mode, or sub-CR clock mode.

bit

7

6

5

4

3

2

1

0

Field

SWT3

SWT2

SWT1

SWT0

MWT3

MWT2

MWT1

MWT0

Attribute

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

1

1

1

1

1

1

1

1

bit7:4

Details

No. of cycles

Subclock (F

CL

) = 32.768 kHz

Writing "1111"

2

15

- 2

(2

15

-2)/F

CL

About 1.0 s

Writing "1110"

2

14

- 2

(2

14

-2)/F

CL

About 0.5 s

Writing "1101"

2

13

- 2

(2

13

-2)/F

CL

About 0.25 s

Writing "1100"

2

12

- 2

(2

12

-2)/F

CL

About 0.125 s

Writing "1011"

2

11

- 2

(2

11

-2)/F

CL

About 62.44 ms

Writing "1010"

2

10

- 2

(2

10

-2)/F

CL

About 31.19 ms

Writing "1001"

2

9

- 2

(2

9

-2)/F

CL

About 15.56 ms

Writing "1000"

2

8

- 2

(2

8

-2)/F

CL

About 7.75 ms

Writing "0111"

2

7

- 2

(2

7

-2)/F

CL

About 3.85 ms

Writing "0110"

2

6

- 2

(2

6

-2)/F

CL

About 1.89 ms

Writing "0101"

2

5

- 2

(2

5

-2)/F

CL

About 915.5 µs

Writing "0100"

2

4

- 2

(2

4

-2)/F

CL

About 427.2 µs

Writing "0011"

2

3

- 2

(2

3

-2)/F

CL

About 183.1 µs

Writing "0010"

2

2

- 2

(2

2

-2)/F

CL

About 61.0 µs

Writing "0001"

2

1

- 2

(2

1

-2)/F

CL

0.0 µs

Writing "0000"

2

1

- 2

(2

1

-2)/F

CL

0.0 µs