MB95630H Series

494

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 24 I

2

C BUS INTERFACE

24.1 Overview

24.1

Overview

The I

2

C bus interface supports the I

2

C bus specification published by Philips.

The interface provides the functions of transmission and reception in master

and slave modes, detection of arbitration lost, detection of slave address and

general call address, generation and detection of start and stop conditions,

bus error detection, and MCU standby wakeup.

■

I

2

C Bus Interface Functions

The I

2

C bus interface is a two-wire, bi-directional bus consisting of a serial data line (SDAn)

and serial clock line (SCLn). The devices connected to the bus via these two wires can

exchange data, and each device can operate as a sender or receiver in accordance with their

respective functions based on the unique address assigned to each device. Furthermore, the

interface establishes a master/slave relationship between devices.

The I

2

C bus interface can connect multiple devices provided the bus capacitance does not

exceed an upper limit of 400 pF. The I

2

C bus interface is a true multi-master bus with collision

detection and a communication control protocol that prevent loss of data even if more than one

master attempts to start a data transfer at the same time.

The communication control protocol ensures that only one master is able to take control of the

bus at a time, even if multiple masters attempt to take control of the bus simultaneously,

without messages being lost or data being altered. Multi-master means that more than one

master can attempt to take control of the bus at the same time without causing messages to be

lost.

The I

2

C bus interface includes a function to wake up the MCU from standby mode.

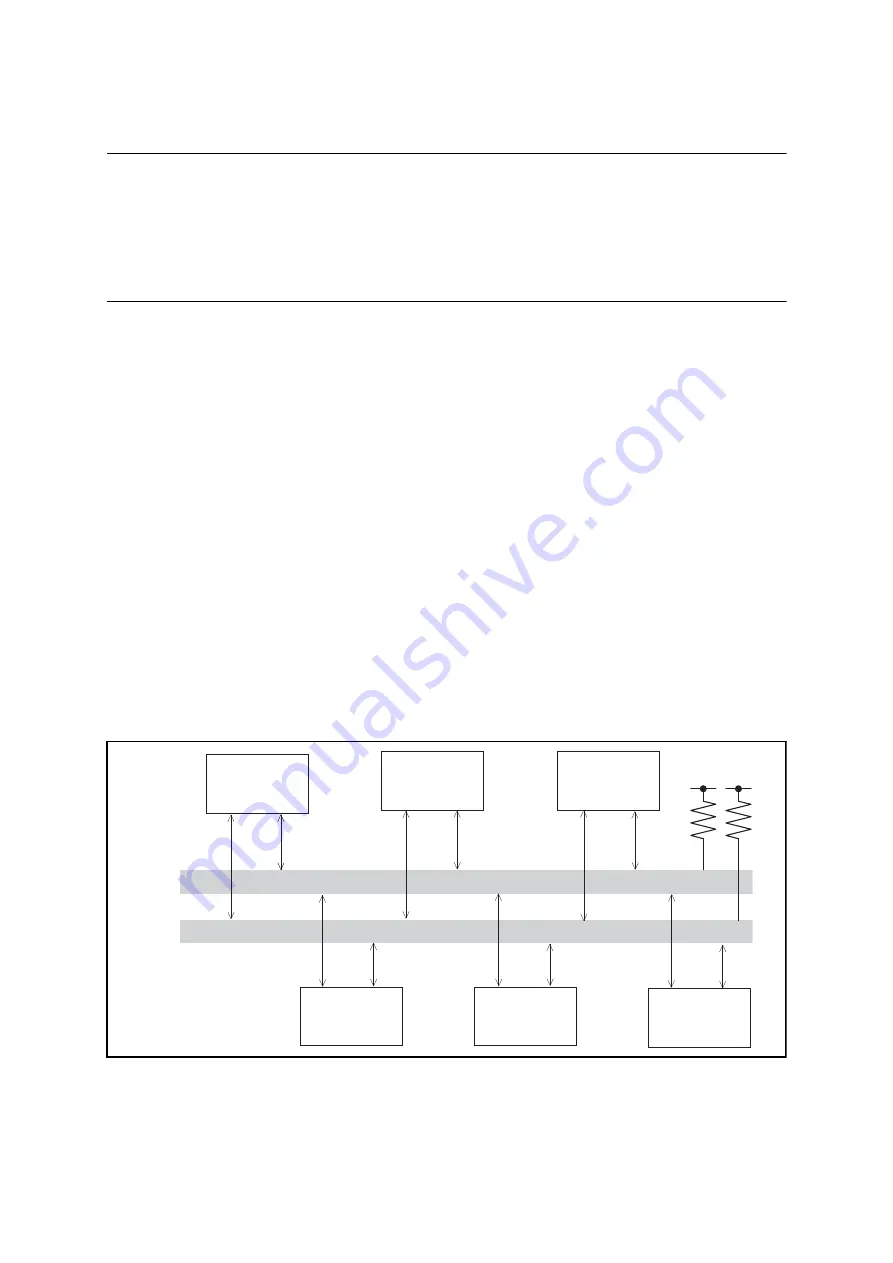

Figure 24.1-1 Example of I

2

C Bus Interface Configuration

S

DAn

S

CLn

Microcontroller

A

LCD driver

S

t

a

tic RAM/

E

2

PROM

G

a

te

a

rr

a

y

A/D converter

Microcontroller

B