MB95630H Series

56

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 3 CLOCK CONTROLLER

3.8 Configuration of Prescaler

3.8

Configuration of Prescaler

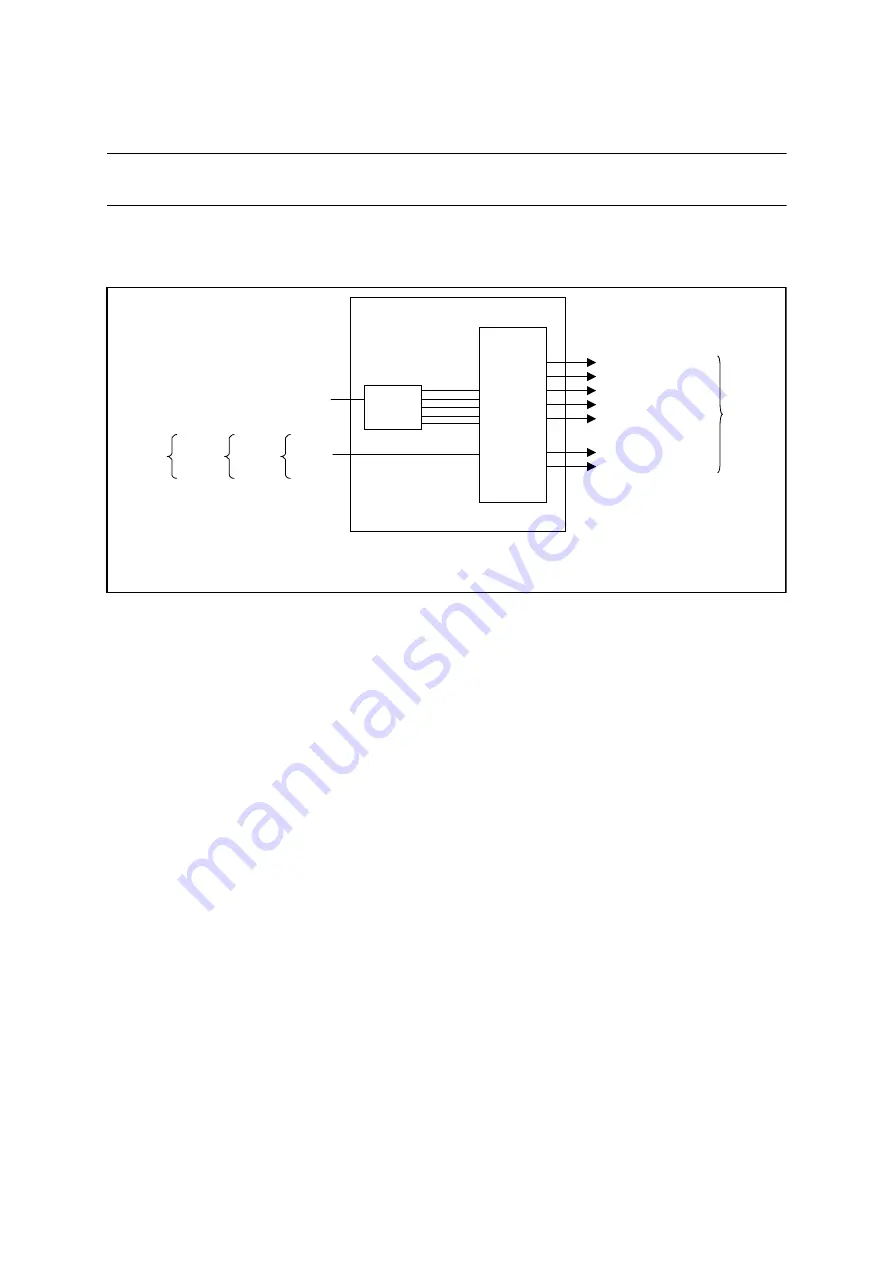

Figure 3.8-1 is the block diagram of the prescaler.

■

Block Diagram of Prescaler

Figure 3.8-1 Block Diagram of Prescaler

•

5-bit counter

This counter counts the machine clock (MCLK) and outputs the count value to the output

control circuit.

•

Output control circuit

Based on the 5-bit counter value, this circuit supplies clocks generated by dividing the

machine clock (MCLK) by 2, 4, 8, 16, or 32 to individual peripheral functions. The circuit

also buffers the clock from the time-base timer (F

CH

/2

7

, F

CH

/2

8

, F

CRH

/2

6

, F

CRH

/2

7

,

F

MCRPLL

/2

6

, or

F

MCRPLL

/2

7

) and supplies it to peripheral functions.

■

Input Clock

The prescaler uses the machine clock, or the output clock of the time-base timer as the input

clock.

■

Output Clock

The prescaler supplies clocks to the following peripheral functions:

•

8/16-bit composite timer

•

8/10-bit A/D converter

•

8/16-bit PPG

•

16-bit PPG timer

•

16-bit reload timer

•

UART/SIO dedicated baud rate generator

MCLK

F

CH

F

CRH

F

MCRPLL

: M

a

chine clock (intern

a

l oper

a

ting fre

qu

ency)

: M

a

in clock fre

qu

ency

: M

a

in CR clock fre

qu

ency

: M

a

in CR PLL clock fre

qu

ency

Pre

s

c

a

ler

O

u

tp

u

t

control circ

u

it

MCLK (m

a

chine clock)

Co

u

nt

clock

s

o

u

rce

to

different

peripher

a

l

f

u

nction

s

5-

b

it

co

u

nter

F

CH

/2

7

, F

CRH

/2

6

or F

MCRPLL

/2

6

MCLK/2

F

CH

/2

8

, F

CRH

/2

7

or F

MCRPLL

/2

7

MCLK/4

MCLK/

8

MCLK/16

MCLK/

3

2

Co

u

nter v

a

l

u

e

F

MCRPLL

/2

6

F

MCRPLL

/2

7

or

F

CH

/2

7

F

CH

/2

8

From

time-

bas

e

timer

F

CRH

/2

6

F

CRH

/2

7

or