5.3 Host Commands

C141-E120-02EN

5-75

•

Error log index

Indicates the latest error log number. If an error has not occurred, 00 is

displayed.

•

Error log 1 to 5

When an error occurs, the error log index value is incremented and

information at the time the error occurred is recorded in the error log area

specified by this value. When the error log index exceeds 05, it returns to 01.

•

Command data 1 to 5

Indicates five commands data in order received by the device until the error

occurs. Commands for which an error occurred are included in Command

Data 5.

•

Error data

Indicates the I/O register values when the error is reported.

•

Status

Bits 0 to 3:

Indicates the drive status when received error commands

according to the following table.

Bits 4 to 7:

Vendor unique

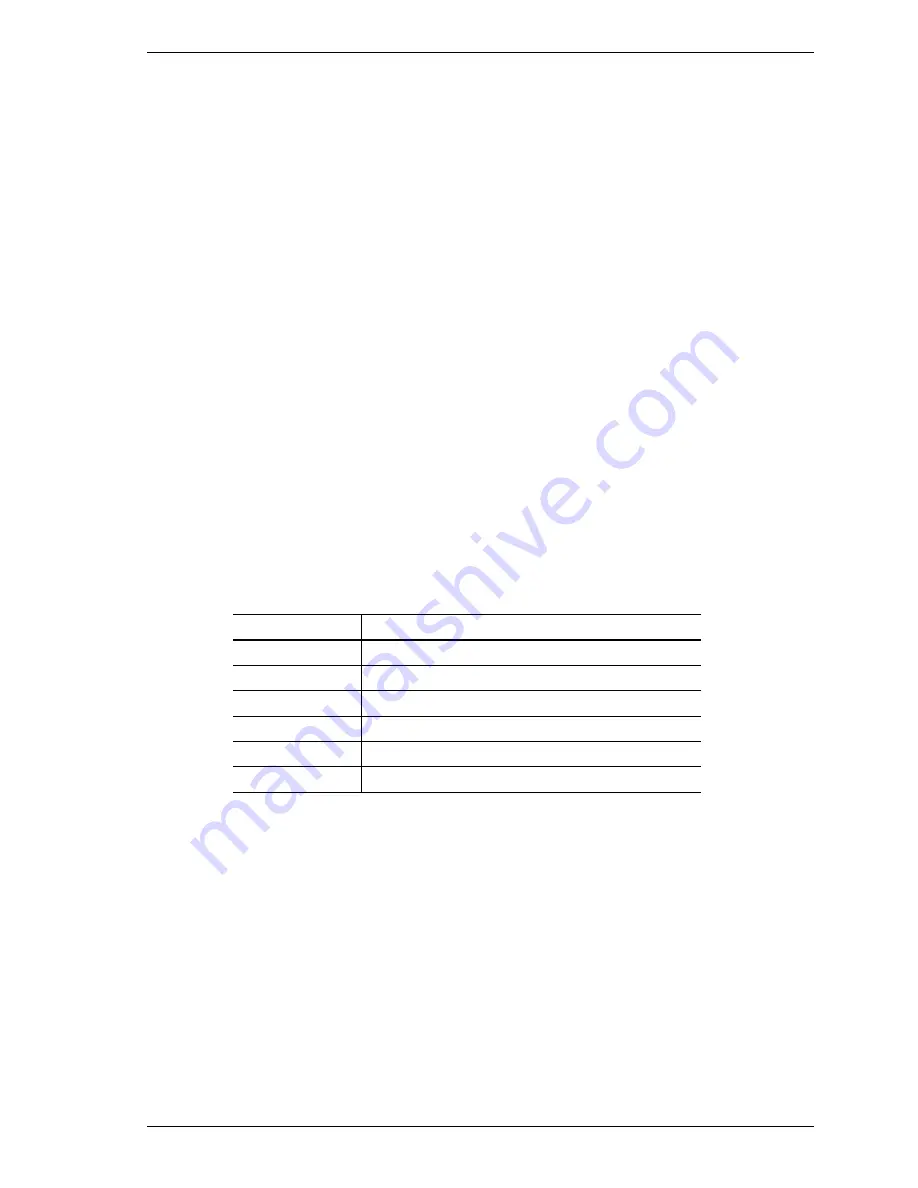

Status

Meaning

0

Unclear status

1

Sleep status

2

Standby status

3

Active status or idle status (BSY bit = 0)

4

Off-line data collection being executed

5 to F

Reserved

•

SMART Self Test

The host computer can issue the SMART Execute Off-line Immediate sub-

command (FR Register = D4h) and cause the device to execute a self test. When

the self test is completed, the device saves the SMART self test log to the disk

medium.

The host computer can issue the SMART Read Log Sector sub-command (FR

Register = D5h, SN Register = 06h) and can read the SMART self test log.

Summary of Contents for MHN2100AT - Mobile 10 GB Hard Drive

Page 1: ...C141 E120 02EN MHN2300AT MHN2200AT MHN2150AT MHN2100AT DISK DRIVES PRODUCT MANUAL ...

Page 4: ...This page is intentionally left blank ...

Page 8: ...This page is intentionally left blank ...

Page 10: ...This page is intentionally left blank ...

Page 12: ...This page is intentionally left blank ...

Page 32: ...This page is intentionally left blank ...

Page 38: ...This page is intentionally left blank ...

Page 52: ...Installation Conditions 3 14 C141 E120 02EN Figure 3 16 Example 2 of Cable Select drive drive ...

Page 58: ...Theory of Device Operation 4 6 C141 E120 02EN Figure 4 3 Circuit Configuration ...

Page 76: ...This page is intentionally left blank ...

Page 174: ...Interface 5 98 C141 E120 02EN g d f f d e Figure 5 7 Normal DMA data transfer ...

Page 224: ...This page is intentionally left blank ...

Page 228: ...This page is intentionally left blank ...

Page 230: ...This page is intentionally left blank ...

Page 232: ...This page is intentionally left blank ...

Page 234: ...This page is intentionally left blank ...

Page 235: ......

Page 236: ......