Interface

5-62

C141-E145-02EN

At command completion (I/O registers contents to be read)

1F7

H

(ST)

Status information

1F6

H

(DH)

x

x

x

DV

xx

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(ER)

xx

xx

xx

xx

Error information

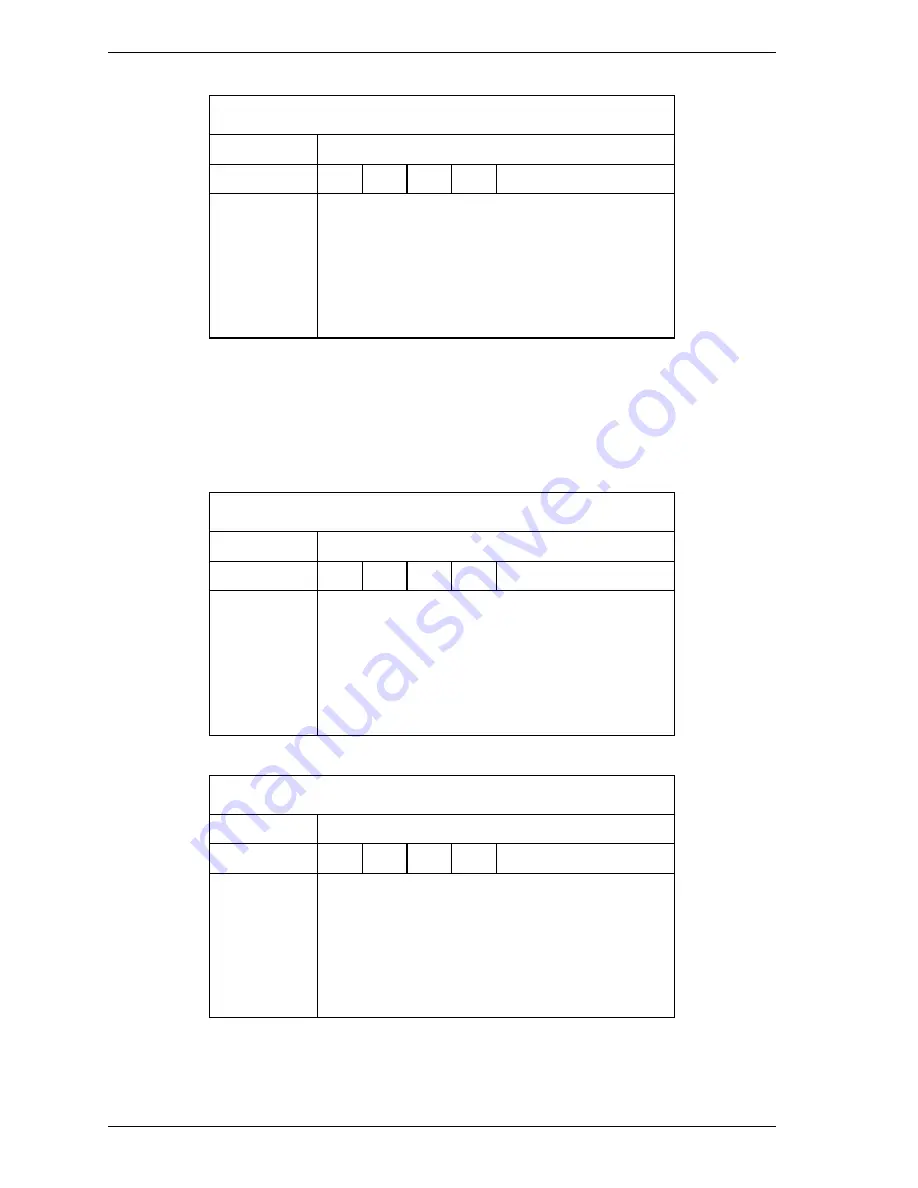

(24) IDLE IMMEDIATE (X’95’ or X’E1’)

Upon receipt of this command, the device sets the BSY bit of the Status register,

and enters the idle mode. Then, the device clears the BSY bit, and generates an

interrupt. This command does not support the automatic power-down function.

At command issuance (I/O registers setting contents)

1F7

H

(CM)

X’95’ or X’E1’

1F6

H

(DH)

x

x

x

DV

xx

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(FR)

xx

xx

xx

xx

xx

At command completion (I/O registers contents to be read)

1F7

H

(ST)

Status information

1F6

H

(DH)

x

x

x

DV

xx

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(ER)

xx

xx

xx

xx

Error information

Summary of Contents for MHR2010AT

Page 1: ...C141 E145 02EN MHR2040AT MHR2030AT MHR2020AT MHR2010AT DISK DRIVES PRODUCT MANUAL ...

Page 4: ...This page is intentionally left blank ...

Page 8: ...This page is intentionally left blank ...

Page 10: ...This page is intentionally left blank ...

Page 12: ...This page is intentionally left blank ...

Page 32: ...This page is intentionally left blank ...

Page 38: ...This page is intentionally left blank ...

Page 58: ...Theory of Device Operation 4 6 C141 E145 02EN Figure 4 3 Circuit Configuration ...

Page 188: ...Interface 5 114 C141 E145 02EN g d f f d e Figure 5 7 Normal DMA data transfer ...

Page 240: ...This page is intentionally left blank ...

Page 242: ...This page is intentionally left blank ...

Page 246: ...This page is intentionally left blank ...

Page 248: ...This page is intentionally left blank ...

Page 249: ......

Page 250: ......