Interface

5-20

C141-E145-02EN

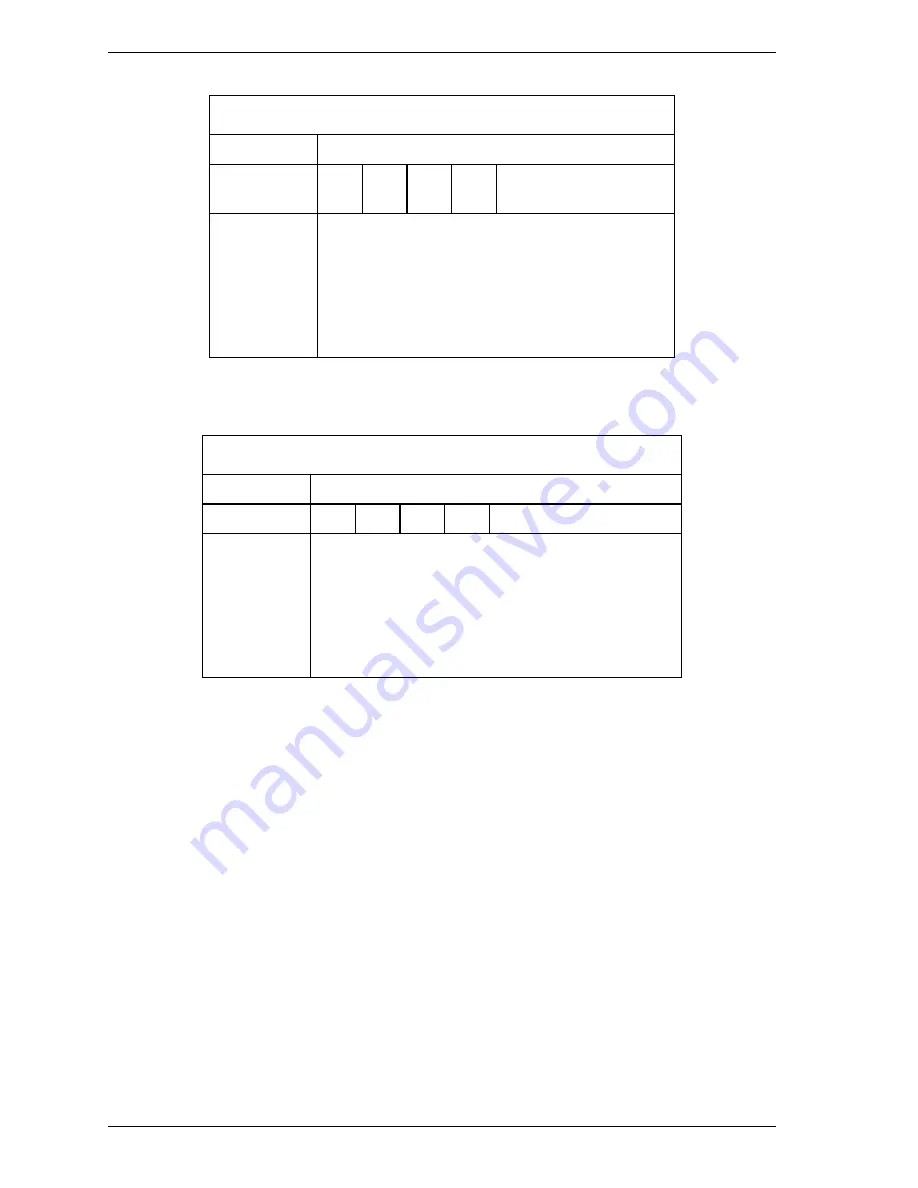

At command issuance (I/O registers setting contents)

1F7

H

(CM)

0

0

1

0

0

0

0

R

1F6

H

(DH)

x

L

x

DV

Start head No. / LBA

[MSB]

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(FR)

Start cylinder No. [MSB] / LBA

Start cylinder No. [LSB] / LBA

Start sector No. / LBA [LSB]

Transfer sector count

xx

(R: Retry)

At command completion (I/O registers contents to be read)

1F7

H

(ST)

Status information

1F6

H

(DH)

x

L

x

DV

End head No. / LBA [MSB]

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(ER)

End cylinder No. [MSB] / LBA

End cylinder No. [LSB] / LBA

End sector No. / LBA [LSB]

00 (*1)

Error information

*1

If the command is terminated due to an error, the remaining number of

sectors of which data was not transferred is set in this register.

(2) READ MULTIPLE (X’C4’)

The READ MULTIPLE Command performs the same as the READ SECTOR(S)

Command except that when the device is ready to transfer data for a block of

sectors, and enters the interrupt pending state only before the data transfer for the

first sector of the block sectors. In the READ MULTIPLE command operation,

the DRQ bit of the Status register is set only at the start of the data block, and is

not set on each sector.

The number of sectors per block is defined by a successful SET MULTIPLE

MODE Command. The SET MULTIPLE MODE command should be executed

prior to the READ MULTIPLE command.

If the number of requested sectors is not divided evenly (having the same number

of sectors [block count]), as many full blocks as possible are transferred, then a

Summary of Contents for MHR2010AT

Page 1: ...C141 E145 02EN MHR2040AT MHR2030AT MHR2020AT MHR2010AT DISK DRIVES PRODUCT MANUAL ...

Page 4: ...This page is intentionally left blank ...

Page 8: ...This page is intentionally left blank ...

Page 10: ...This page is intentionally left blank ...

Page 12: ...This page is intentionally left blank ...

Page 32: ...This page is intentionally left blank ...

Page 38: ...This page is intentionally left blank ...

Page 58: ...Theory of Device Operation 4 6 C141 E145 02EN Figure 4 3 Circuit Configuration ...

Page 188: ...Interface 5 114 C141 E145 02EN g d f f d e Figure 5 7 Normal DMA data transfer ...

Page 240: ...This page is intentionally left blank ...

Page 242: ...This page is intentionally left blank ...

Page 246: ...This page is intentionally left blank ...

Page 248: ...This page is intentionally left blank ...

Page 249: ......

Page 250: ......