C141-E112-01EN

5 - 22

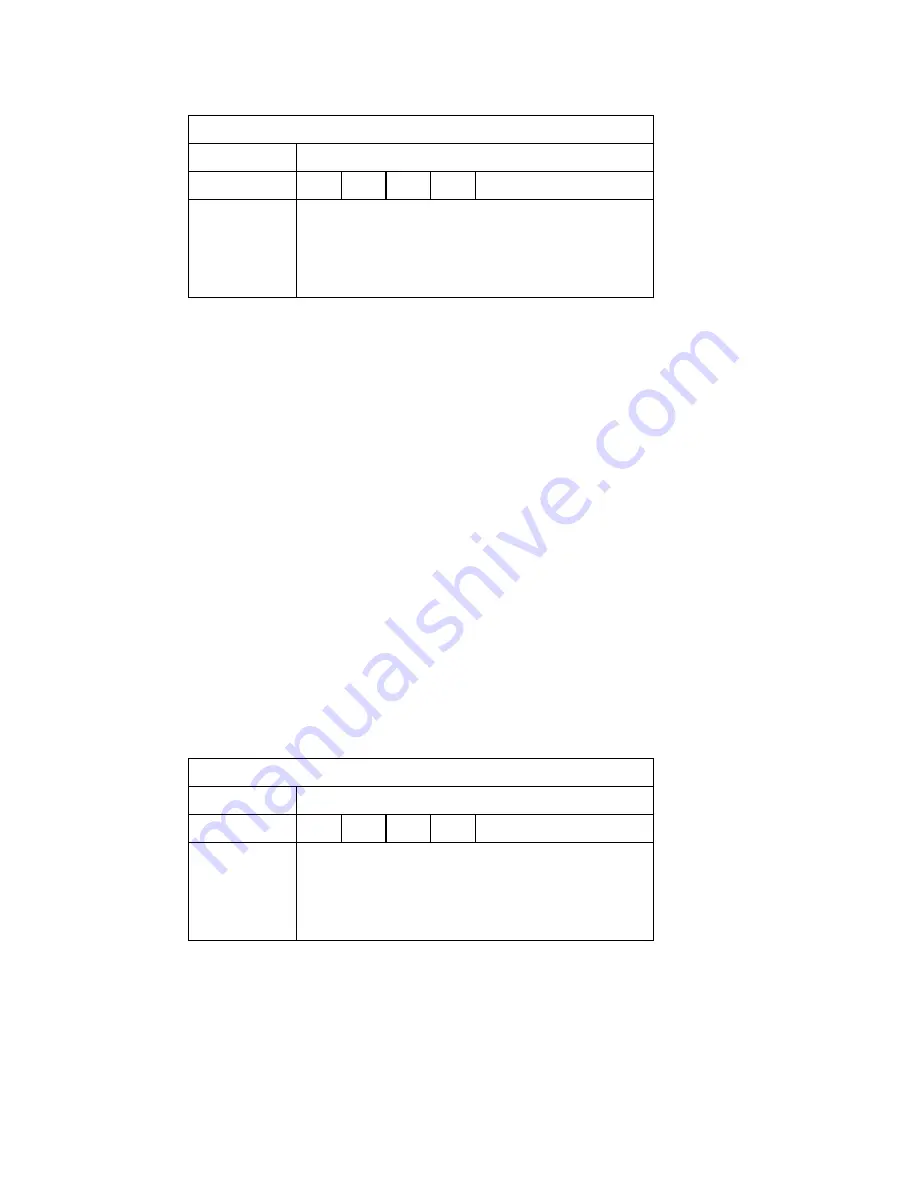

At command completion (I/O registers contents to be read)

1F7

H

(ST)

Status information

1F6

H

(DH)

×

L

×

DV

End head No. /LBA [MSB]

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(ER)

End cylinder No. [MSB] / LBA

End cylinder No. [LSB]

/ LBA

End sector No.

/ LBA [LSB]

00 (*1)

Error information

*1 If the command is terminated due to an error, the remaining number of

sectors of which data was not transferred is set in this register.

(5)

WRITE SECTOR(S) (X'30' or X'31')

This command writes data of sectors from the address specified in the Device/Head, Cylinder

High, Cylinder Low, and Sector Number registers to the address specified in the Sector Count

register. Number of sectors can be specified to 256 sectors in maximum. Data transfer begins at

the sector specified in the Sector Number register. For the DRQ, INTRQ, and BSY protocols

related to data transfer, see Subsection 5.4.2.

If the head is not on the track specified by the host, the device performs a implied seek. After the

head reaches to the specified track, the device writes the target sector.

The data stored in the buffer, and CRC code and ECC bytes are written to the data field of the

corresponding sector(s). Upon the completion of the command execution, the command block

registers contain the cylinder, head, and sector addresses of the last sector written.

If an error occurs during multiple sector write operation, the write operation is terminated at the

sector where the error occurred. Command block registers contain the cylinder, the head, the

sector addresses (in the CHS mode) or the logical block address (in the LBA mode) of the sector

where the error occurred. Then the host can read the command block registers to determine what

error has occurred and on which sector the error has occurred.

At command issuance (I/O registers setting contents)

1F7

H

(CM)

0

0

1

1

0

0

0

R

1F6

H

(DH)

×

L

×

DV

Start head No. /LBA [MSB]

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(FR)

Start cylinder No. [MSB] / LBA

Start cylinder No. [LSB] / LBA

Start sector No.

/ LBA [LSB]

Transfer sector count

xx

R = 0 or 1

Summary of Contents for MPG3102AH

Page 1: ...C141 E112 01EN MPG3xxxAH DISK DRIVES PRODUCT MANUAL ...

Page 3: ...This page is intentionally left blank ...

Page 5: ...This page is intentionally left blank ...

Page 9: ...This page is intentionally left blank ...

Page 17: ...This page is intentionally left blank ...

Page 33: ...C141 E112 01EN 3 2 Figure 3 1 Dimensions ...

Page 195: ......