C141-E110-02EN

6 - 18

(3)

Full hit (hit all)

All requested data are stored in the data buffer. The disk drive starts transferring the requested

data from the address of which the requested data is stored. After completion of command, a

previously existed cache data before the full hit reading are still kept in the buffer, and the disk

drive does not perform the read-ahead operation. If the disk drive receives a full hit command

while performing the read-ahead operation, the disk drive starts transfering the requested data

without stopping the read-ahead operation.

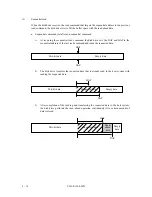

1) In the case that the contents of the data buffer is as follows for example and the previous

command is a sequential read command, the disk drive sets the HAP to the address of which

the hit data is stored.

HAP (set to hit position for data transfer)

Last position at previous read command

Last position at previous read command

Cache data

Full hit data

Cache data

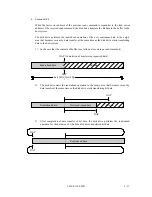

2) The disk drive transfers the requested data but does not perform the read-ahead operation.

(stopped)

HAP

Cache data

Full hit data

Cache data

(4)

Partially hit

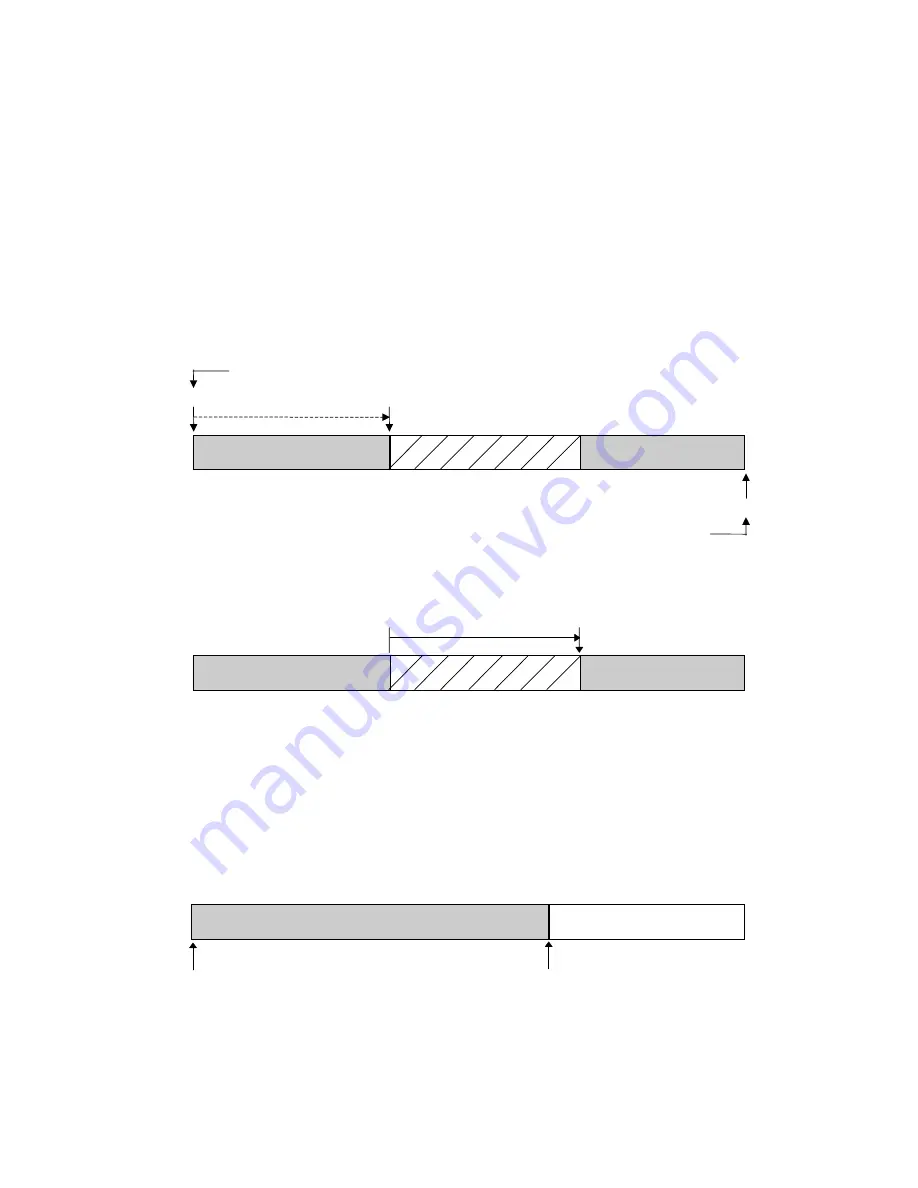

A part of requested data including a lead sector are stored in the data buffer. The disk drive starts

the data transfer from the address of the hit data corresponding to the lead sector of the requested

data, and reads remaining requested data from the disk media directly.

Following is an example of partially hit to the cache data.

Last LBA

Cache data

DAP

HAP

Start LBA

Summary of Contents for MPG3xxxAT

Page 1: ...C141 E110 02EN MPG3xxxAT DISK DRIVES PRODUCT MANUAL ...

Page 3: ...This page is intentionally left blank ...

Page 15: ...This page is intentionally left blank ...

Page 31: ...C141 E110 02EN 3 2 Figure 3 1 Dimensions ...

Page 47: ...This page is intentionally left blank ...

Page 67: ...This page is intentionally left blank ...

Page 177: ...This page is intentionally left blank ...

Page 201: ......