Pin-out and Signal Description

GS2011M Low Power WiFi Module Data Sheet

GS2011Mxx Device Pin-out

42

Confidential

Preliminary

GS2011M-DS-001211, Release 0.9

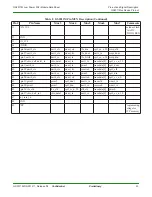

GS2011M Pin MUX Function

The GS2011M pins have multiple functions that can be selected using MUX function by

software. Each pin has an independent MUX select register.

various MUX functions for each pin. All pins are GPIO inputs at reset. For pins that are

inputs to functional blocks only one pin may be assigned to any input function. For

example, UART1_RX may be assigned to GPIO3 but not to both GPIO3 and GPIO37.

Table 8 GS2011M Pin MUX Description

Pin#

Pin Name

Mux3

Mux4

Mux5

Mux6

Mux7

Comments

1

GND

2

jtag_tck

3

jtag_tdo

4

jtag_tdi

5

jtag_tms

6

jtag_trst_n

7

rtc_io_1

8

rtc_io_0

9

VRTC

10

dc_dc_cntl/rtc_io_4

11

adc_sar_0

12

adc_sar_1

13

rtc_io_2

14

gpio6/spi1_din

spi1_din

wspi_din

spi1_dout

wspi_dout

spi0_cs_n_1

15

gpio7/spi1_dout

spi1_dout

wspi_dout

spi1_din

wspi_din

spi0_cs_n_2

16

VOUT_1V8

17

GND

18

gpio5/spi1_clk

spi1_clk

wspi_clk

pwm0

traceclk

spi0_cs_n_3

19

gpio4/spi1_cs_n_0

spi1_cs_n_0 wspi_cs_n_0

spi0_cs_n_4 reserved

clk_rtc

20

gpio13/spi1_cs_n_1

spi1_cs_n_1 pwm2

spi0_cs_n_5 tracedata[0]

wspi_cs_n_1

21

gpio21/clk_rtc

clk_rtc

spi1_cs_n_2

clk_hs_xtal tracedata[1]

spi0_cs_n_6

22

gpio20/clk_hs_rc

clk_hs_rc

spi1_cs_n_3

clk_hs_xtal tracedata[2]

spi0_cs_n_7

23

gpio19_clk_hs_xtal

clk_hs_xtal gpi1_cs_n_4

pwm2

tracedata[3]

spi0_cs_n_8

24

gpio10/pwm0

pwm0

reserved

reserved

tracedata[0]

clk_rtc

25

gpio9/i2c_clk

i2c_clk

uart1_rx

reserved

tracedata[1]

i2s_lcrclk

26

gpio8/i2c_data

i2c_data

uart1_tx

reserved

tracedata[3]

reserved

27

gpio36/sdio_dat0/spi0_dout

sdio_data0

reserved

i2c_data

reserved

spi0_dout

28

gpio35/sdio_clk/spi0_clk

sdio_clk

reserved

i2c_clk

traceclk

spi0_clk

Note: only

4mA for i2c

29

gpio33/sdio_dat3/spi0_cs_n_0 sdio_data3

reserved

uart1_rts

tracedata[0]

spi0_cs_n_0

30

gpio34/sdio_cmd/spi0_din

sdio_cmd

reserved

uart1_cts

tracedata[1]

spi0_din