Minimal Design for GR551x SoC

3

Minimal Design for GR551x SoC

The absolute necessary sections required for the GR551x SoC minimal system operation include

•

Power supply

•

Clock

•

RF

•

I/O pins

•

SWD interfaces

To ensure the proper operation of a GR551x SoC, the design guidelines for the schematic diagram and the PCB layout

are illustrated in the following sections.

3.1 Schematic Design Guideline

For the minimal schematic for a GR551x SoC, see “

”.

3.1.1 Power Supply

3.1.1.1 Introduction

GR551x SoCs are powered by external power sources through VBATL (voltage range: 1.7 V to 3.8 V).

To optimize battery utilization, it is recommended to supply a GR551x SoC with an external LDO regulator with low

quiescent current (Ig) (lower than the product current when product is in standby mode) (output voltage: ≤ 3.3 V,

output current: > 100 mA, load regulation (Iout: 10% – 120%) ≤ 10 mA).

When the maximum input level of the LDO regulator is higher than 5.5 V, connect a resistor (0.39 Ω – 1 Ω) in series to

the input end of the LDO regulator to avoid overshoot when powering on the GR551x SoC in operation.

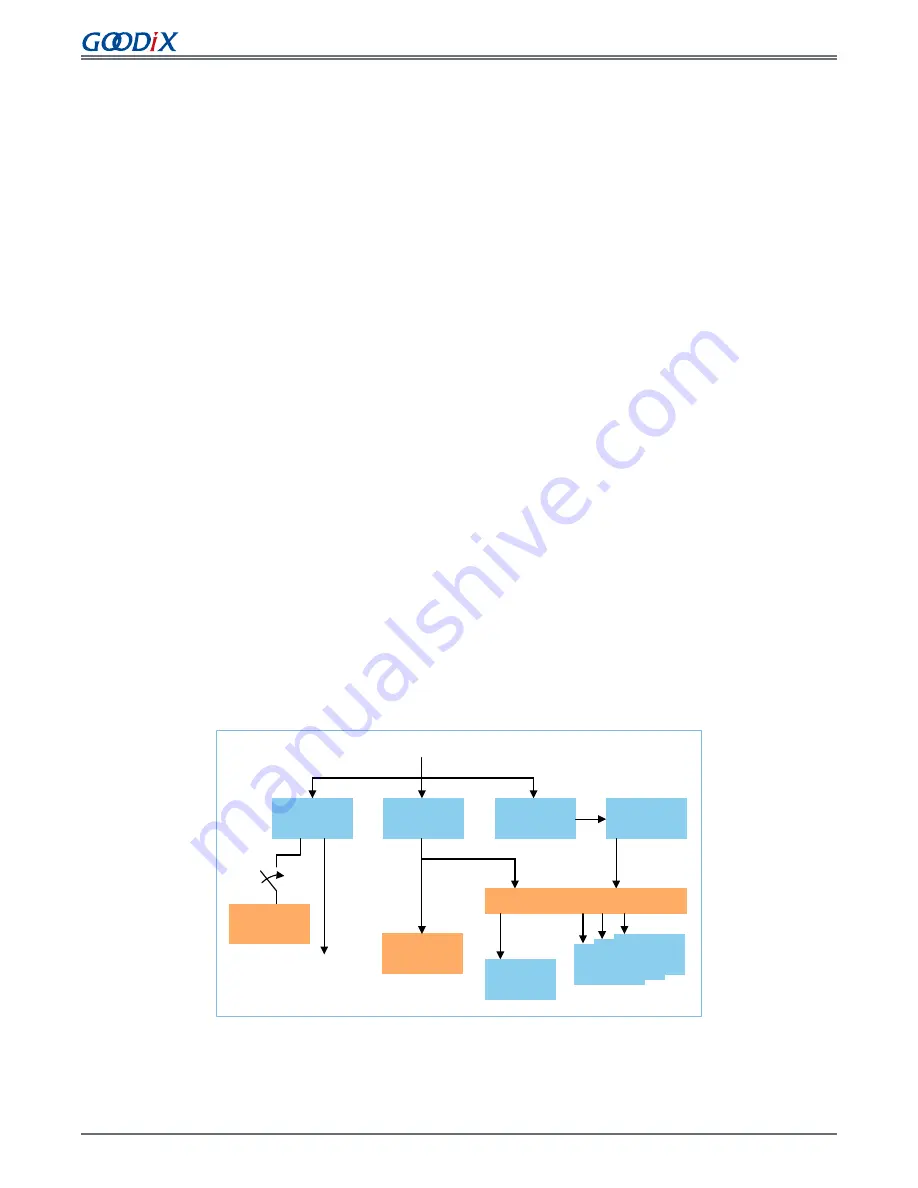

shows the power management unit in a GR551x.

Power

Island #1

Power

Island #1

Power

Island #1

Power

Island #n

Always ON

Power Island

¼

¼

Control Switch

Low Power

LDO

DC-DC

Digital LDO

V

BATT

V

DD

IO

LDO

Stacked

Flash

V

RET

VDDIO

Figure 3-1 Power management block diagram

Copyright © 2021 Shenzhen Goodix Technology Co., Ltd.

22