2 Introduction

2.4 Resource Utilization

IPUG781-1.5.1E

5(12)

Device

7.2.3

Suspended Low-power

Device

I

CCSL

Section 7.2.3

500

µA

2.4

Resource Utilization

Gowin USB 2.0 SoftPHY IP can be implemented by Verilog. Its

resource utilization may vary when the design is employed in different

devices, or at different densities, speeds, or grades. Taking Gowin

GW1NSR-4 and GW2AR-18 series of FPGA ptoducts as an instance, the

resource utilization is as shown in Table 2-3 and Table 2-4.

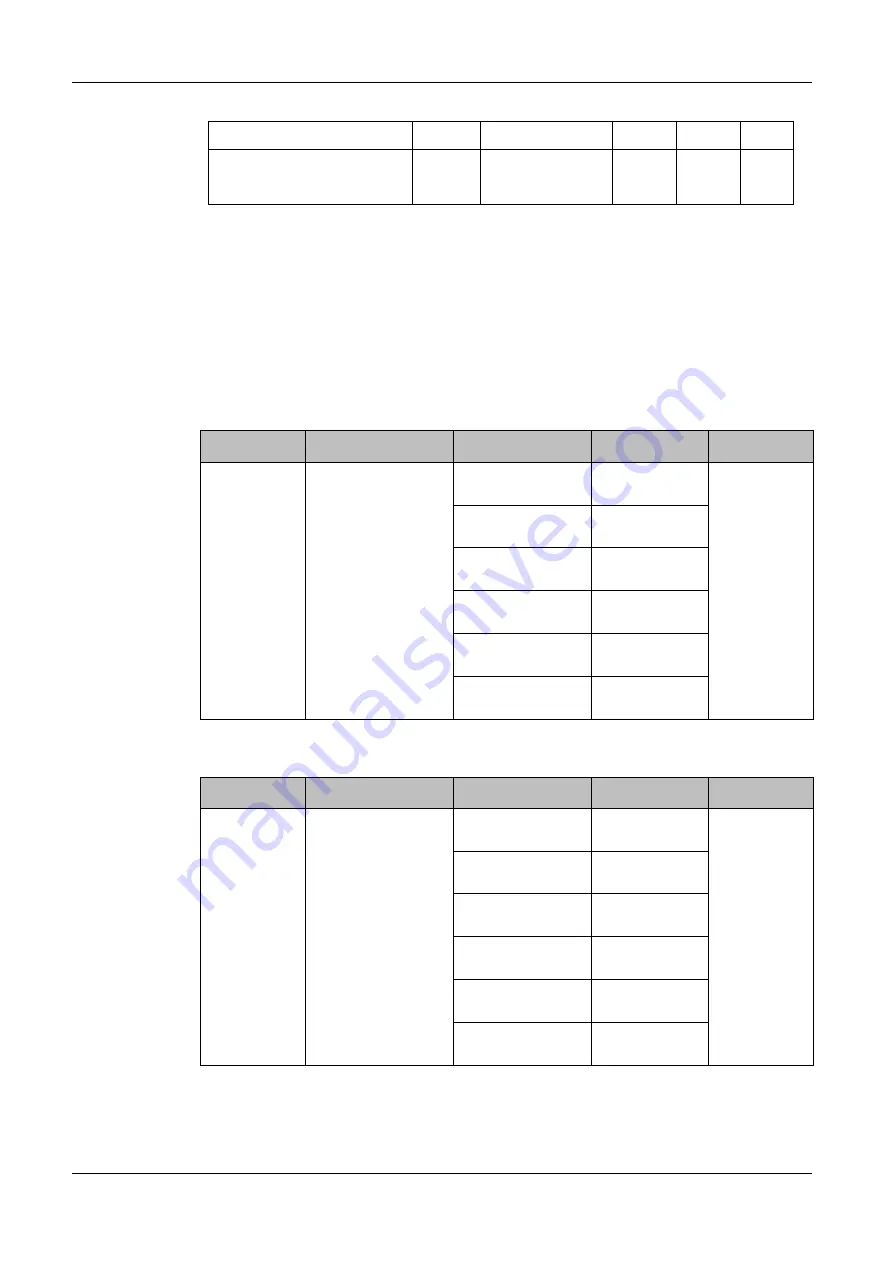

Table 2-3 Resource Utilization (І)

Device

Speed Grade

Resource

Utilization

Notes

GW1NSR-4

C7/I6

LUT

384

-

REG

1109

ALU

13

BSRAM

1

SSRAM

0

IO

7

Table 2-4 Resource Utilization (

Ⅱ

)

Device

Speed Grade

Resource

Utilization

Notes

GW2AR-18

C7/I6

LUT

384

-

REG

1109

ALU

13

BSRAM

1

SSRAM

4

IO

7

Note!

GW2A series and GW1NSR-4 can choose the chip with speed grade C6/I5; for other part

numbers, please choose the chip with speed grade C7/I6.