2 Introduction

2.1 Overview

IPUG781-1.5.1E

3(12)

2

Introduction

2.1

Overview

Gowin USB 2.0 SoftPHY IP is a USB physical layer transceiver that can

support data reception and transmission at high speed (480Mbps), full

speed (12Mbps), and low speed (1.5Mbps).

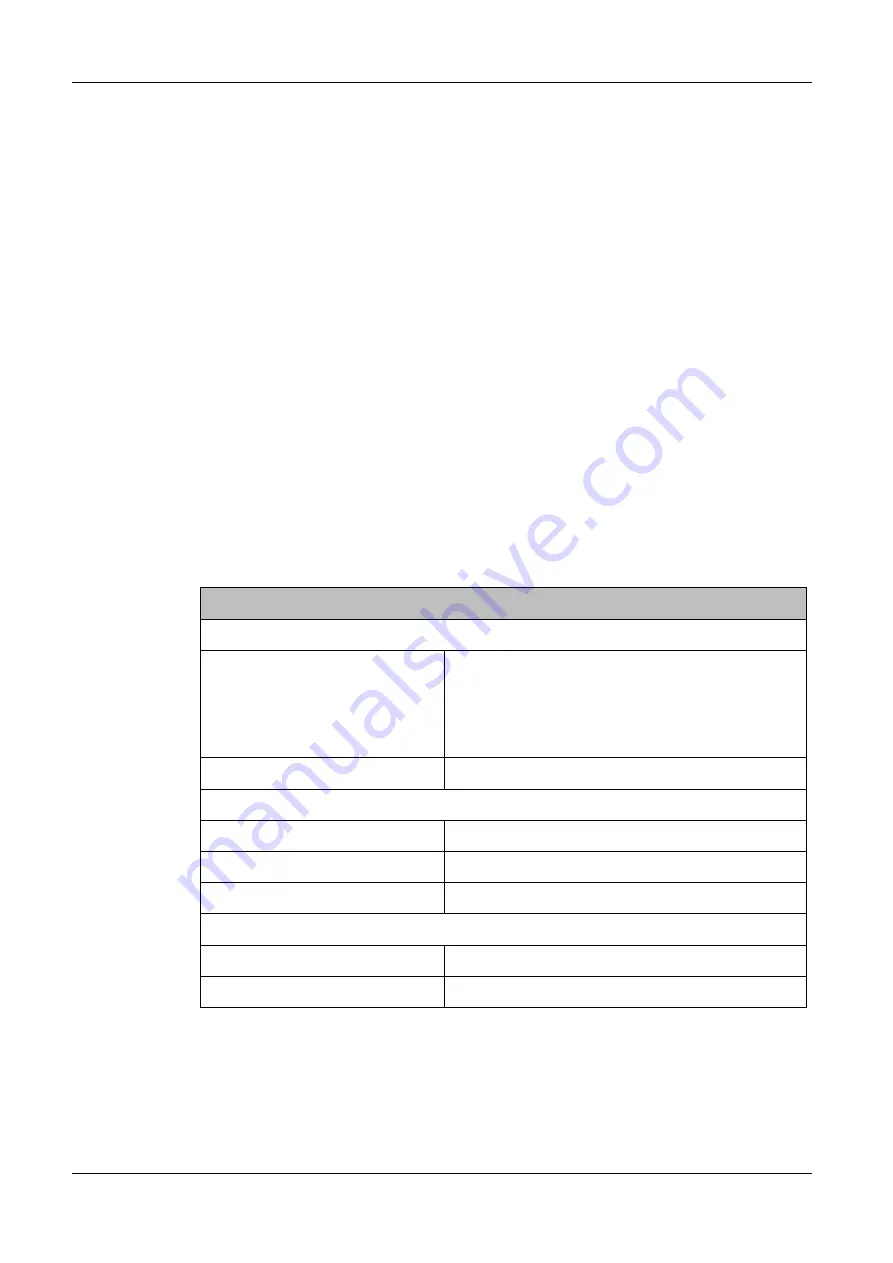

Table 2-1 Gowin USB 2.0 SoftPHY IP Overview

Gowin USB 2.0 SoftPHY IP

IP Core Application

Supported Devices

[1]

Arora family

LittleBee family, excluding

GW1N-1/GW1N-1S/GW1NZ-1/GW1N-1P5

devices..

Logic Resource

Please refer to Table 2-3 and Table 2-4.

Delivered Doc.

Design Files

Verilog (encrypted)

Reference Design

Verilog

TestBench

Verilog

Test and Design Flow

Synthesis Software

GowinSynthesis

Application Software

Gowin Software (V1.9.8.05 and above)

Note!

[1] Only part number with speed grade C7 and above support USB 2.0 SoftPHY IP