2 Introduction

2.2 Features

IPUG781-1.5.1E

4(12)

2.2

Features

The features of GowinUSB 2.0 SoftPHY IP include:

Supports HS (480 Mbps), FS (12 Mbps), and LS (1.5 Mbps).

Supports data serial and parallel conversion.

Supports bit stuffer and unstuffer.

Supports NRZI encoder and decoder.

Supports UTMI interface.

2.3

Using 5V Host Supply to Power USB Device Solution

Many solutions may to provide power to a USB device using the 5V

provided over the cable from the Host without providing a separate power

supply. To support cable powered USB device use cases, designers must

be careful to ensure the total PCB BOM of the device does not exceed the

current limitations of the USB Host as well as voltage drops over the cable.

The USB v2.0 specification, sections 7.1.2 and 7.3.2 provides

information on current and voltage drop requirements expected to be

supplied by a USB Host. If the total PCB BOM cannot meet the current and

minimum voltage requirements of the specified host, the board can be

powered with a separate power supply.

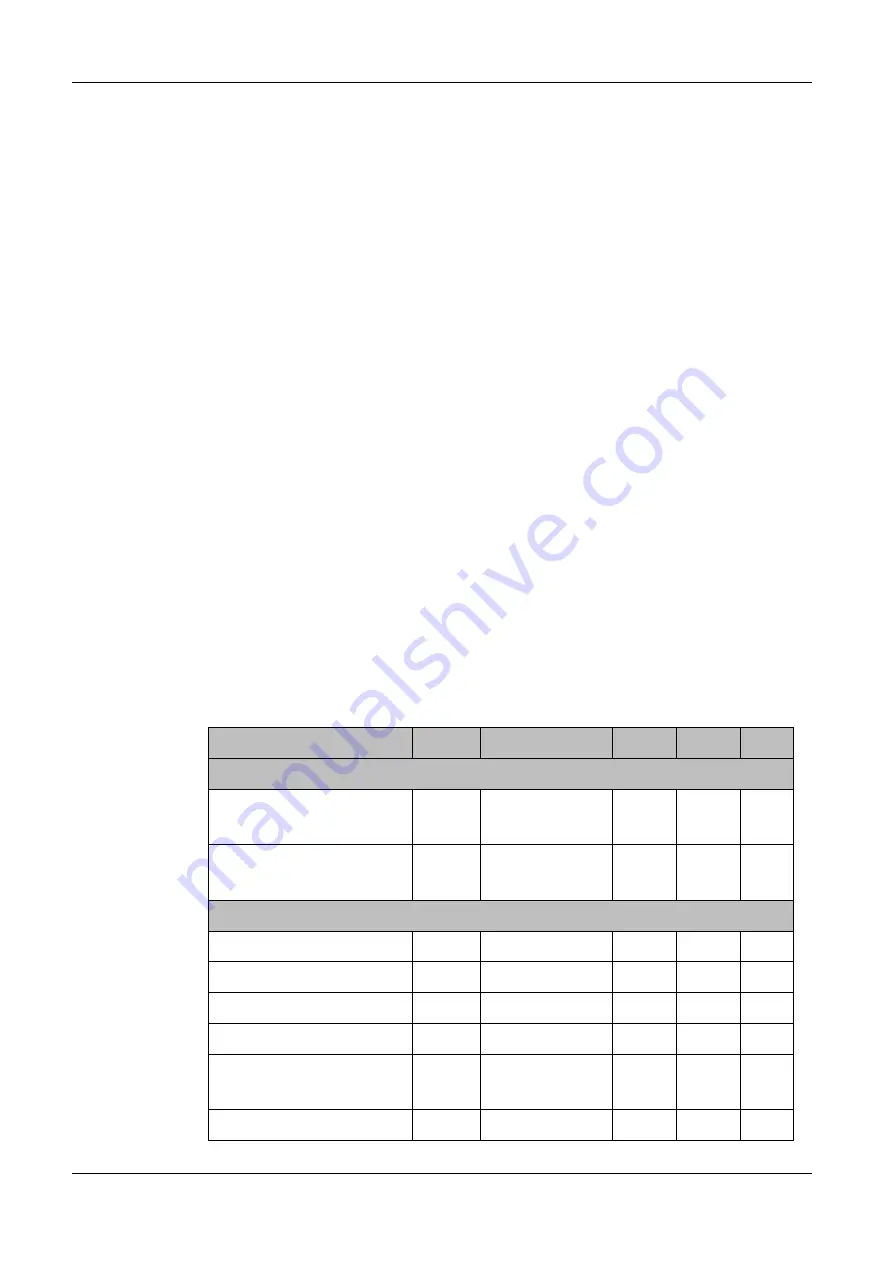

Table 2-2 DC Electrical Characteristics

Parameter

Symbol Condition

Min.

Max.

Unit

Supply voltage

High-power Port

V

BUS

Note 2, Section

7.2.1

4.75

5.25

V

Low-power Port

V

BUS

Note 2, Section

7.2.1

4.40

5.25

V

Supply Current

High-power Hub Port (out)

I

CCPRT

Section 7.2.1

500

mA

Low-power Hub Port (out)

I

CCUPT

Section 7.2.1

100

mA

High-Power Function (in)

I

CCHPF

Section 7.2.1

500

mA

Low-power Function (in)

I

CCLPF

Section 7.2.1

100

mA

Unconfigured

Function/Hub (in)

I

CCINIT

Section 7.2.1.4

100

mA

Suspended High-power

I

CCSH

Note 15, Section

2.5

mA