k

2 - 16

GRUNDIG Service

Descriptions

TVR 3710 …, TVR 5100 …,TVR 5500 …

the "IN/OUT" circuit stage to the TV Signal Electronics and the EURO-

AV socket respectively.

On "LP" mode, switchover of the equalizing circuit is carried out by the

switch EP CTL.

3.7.4 Muting Circuit

The mute command (MTA) from the deck computer IC7410-(40) mutes

the audio outputs of IC7601 in all functions, with the exception of

playback and record, and also in the case of servo faults. For this, the

IC7601 obtains the mute command "MTA" via pin 22 (HIGH active).

word corresponding to the brightness information and is present at

the output of the ROM after every 1

µ

s. This data word is entered into

a shift register and is read out at a 12MHz pixel clock derived from

the 6MHz clock. The corresponding R/G/B signals are available at

the push-pull outputs IC7880-(15…17). The maximum output level

of the R/G/B signals is determined by the voltage present on

IC7880-(18). The blank signal from IC7880-(19) is used to control

the insertion of the R/G/B signals in IC7200 within the TV Signal

Electronics (signal chassis).

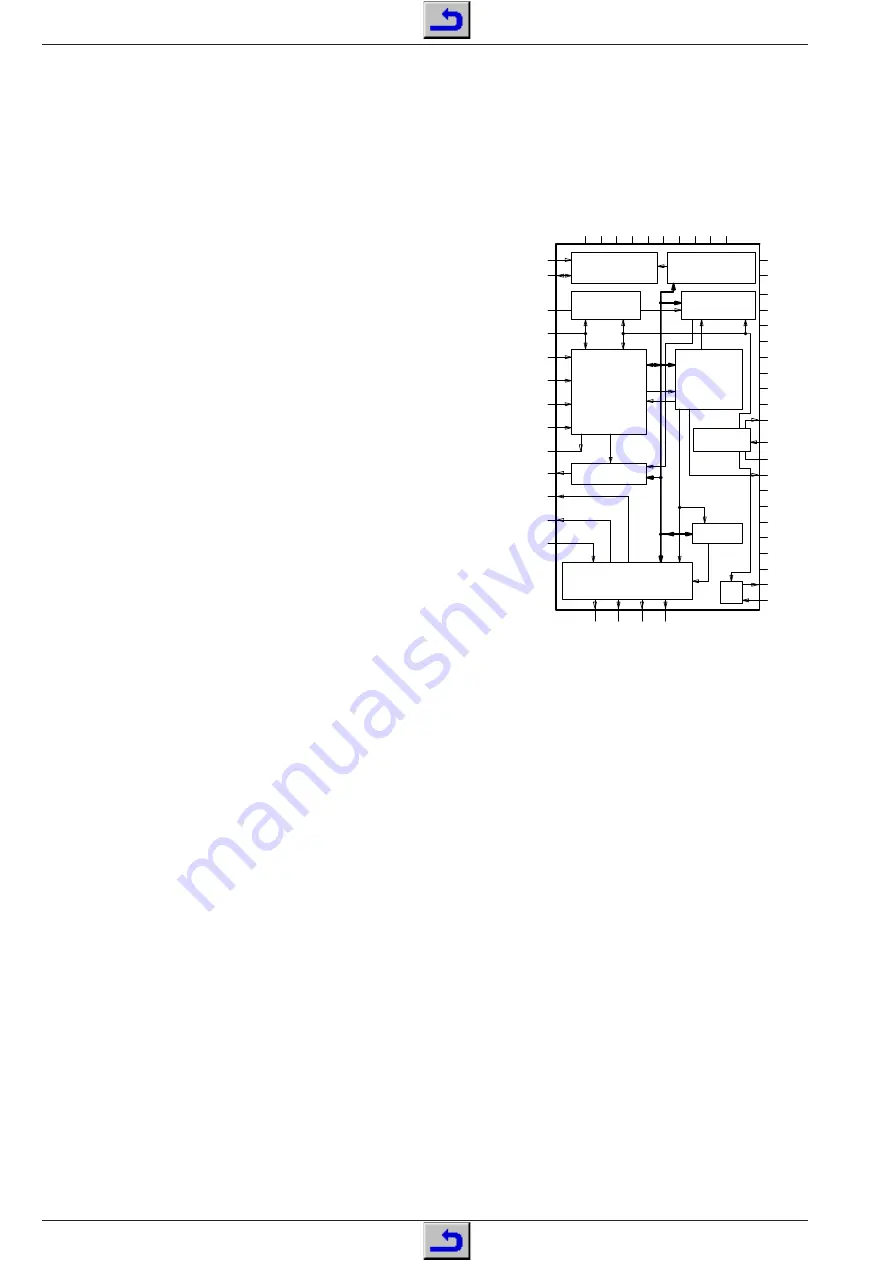

4. Teletext "DOS" (TXT)

Function Overview

The DOS unit contains a Test Pattern / Data Generator and the VPS/

PDC/Teletext processing stage with IC7881 or IC7880 (with VPS and

PDC processing) being the heart of it. The following description refers

to IC7880. This IC7880, named IVT (Integrated Video-Input-Processor

and Teletext) includes the following function groups:

– Data Slicer

The adaptive data slicer extracts the VPS/PDC/teletext data from

the CCVS signal (VTV) fed in via IC7880-(8). For this, the video

signal is taken to an A/D converter. The text data is then separated

and the appropriate clock (6.9375MHz for PDC/Teletext and

2.5MHz for VPS ) is generated from the digitised video signal. The

black level of the CCVS signal is stored by C2888 at IC7880-(7). The

reference current for analog signal processing is derived via

IC7880-(9).

– Clock-PLL

The free-running 27MHz oscillator frequency is determined by the

quartz Q1800 at IC7880-(2…4) and is used first of all for the A/D

converter. Secondly, a digital PLL generates from it the basic

frequencies 6MHz, 1MHz, and 15.625kHz. The generated line

frequency is then fed to a phase comparator along with the line sync

signals separated from the CCVS signal. The characteristic of the

digital loop filter which follows is influenced by a control register and

the 6MHz oscillator is controlled accordingly. By this method, all

frequencies generated in the IVT are synchronized to the line

frequency of the incoming CCVS signal. In unsynchronized condi-

tion (eg. test pattern) no phase comparison takes place.

– I

2

C-bus Interface

This interface permits the central computer (IC7880) to control all

operations and also to read data into and out of each storage

location of the page memory.

– Control Logic

The control logic consists of various counters, gate circuits and

control registers which can be controlled via the I

2

C-bus. The control

logic is supplied with the internally generated 6MHz, 1MHz, H and

V-frequency pulses. In this way, the sync signal (IC7880-(12)), the

pixel clock for the character generator, and the control signals for the

page memory interface are produced among others.

– Data Acquisition

During the lines 16 for VPS, 2…22 and 315…335 for PDC/Teletext

the control logic provides a so-called data input window. The

acquisition circuit identifies the corresponding data by a determined

frame code. Subsequently, the data is subjected to a serial/parallel

conversion and an error detection or correction. When the user calls

up a text page a register with the page number is loaded via the I

2

C-

bus. The acquisition circuit then compares all incoming page num-

bers with the requested page and initializes the storage of the page

in the page memory.

– Page Memory

The 8k x 8-DRAM is used to store up to 8 teletext pages as well as

the PDC and VPS data.

– Character Generator

There are 256 different characters. Each of these characters is

allocated a 8bit data word. Apart from 32 control characters, the set

consists of graphic or alphanumeric characters composed in the

form of a raster point matrix of 12 horizontal and 10 vertical points.

The characters are stored in the Character ROM in the IVT. The line-

coupled 1MHz clock is used to switch the addresses fed in to the

page memory. The 8bit code representing the respective character

in turn forms one part of the address fed in to the character ROM. The

other part is produced by a line counter. The result is a 12bit data

IC7880

SAA5281

Line Counters

and Display

Acquisition

Oscillator

/2

8k Memory

Character Generator Buffers

Character ROM

ODD/EVEN OR DV

Digital PLL

and processing

Sync separation

and Acquisition

Data slicing

AD-Conversion

Clamp

Control Registers

I2C Businterface

37

38

39

40

41

42

43

44

45

46

47

48

1

2

3

4

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36