GV-395 Virtex-II DSP Hardware Accelerator Manual

GV & Associates, Inc.

07/10/04

25

11.0

DPX FPGA (U16)

11.1

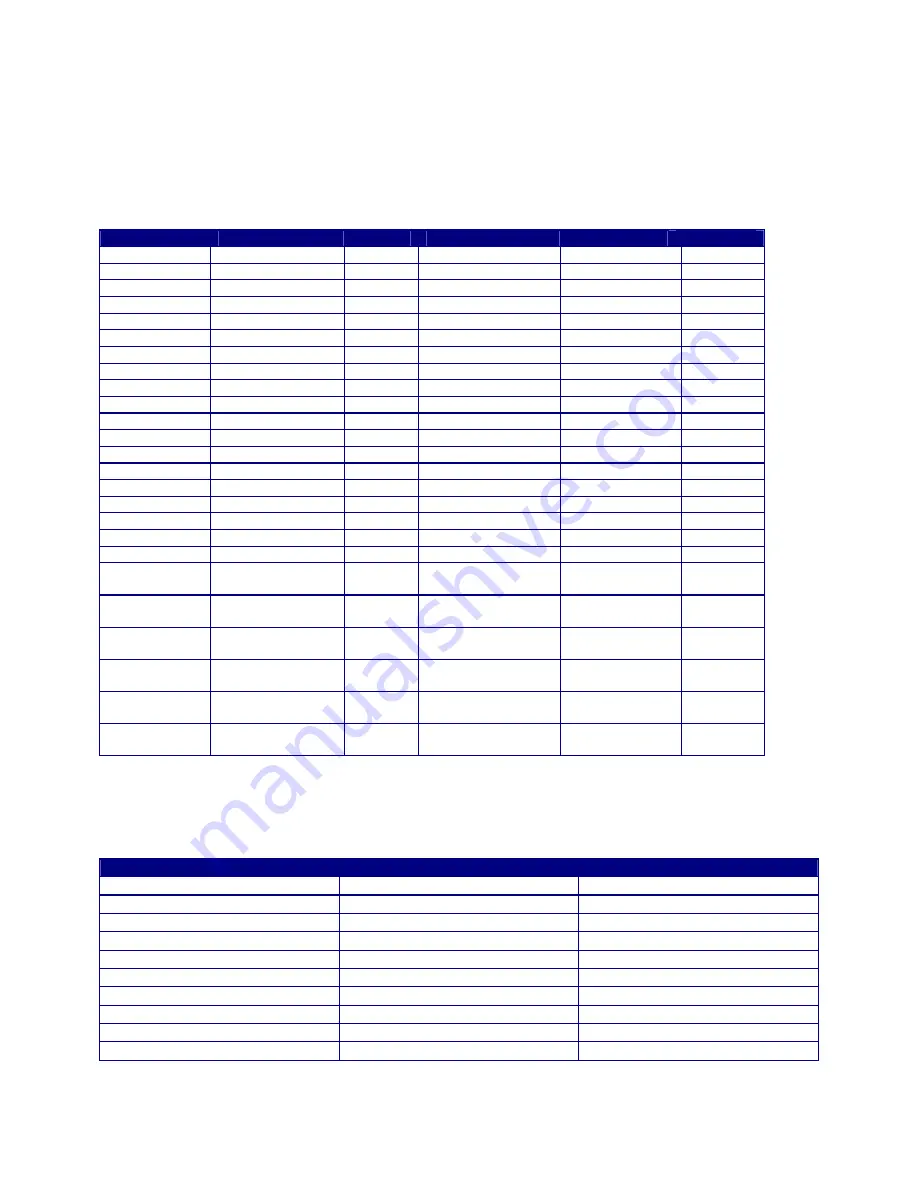

DPX FPGA 4 X 1M X 16 ZBT RAM

DPX Virtex-II FPGA has access to four 1M x 18 ZBT RAMs. The access time for DPX Static RAM is 10

nanoseconds. Refer to the data sheet for the IDT71T75802 for more detailed information. The interconnection is

shown in the table below.

Description

Signal

Pin No.

Description

Signal

Pin No.

Address Bit 0

ZBTM_A0

A31

Data Bit 0

ZBTM_D0

A12

Address Bit 1

ZBTM_A1

A30

Data Bit 1

ZBTM_D1

A11

Address Bit 2

ZBTM_A2

A28

Data Bit 2

ZBTM_D2

A9

Address Bit 3

ZBTM_A3

A29

Data Bit 3

ZBTM_D3

A7

Address Bit 4

ZBTM_A4

A26

Data Bit 4

ZBTM_D4

A6

Address Bit 5

ZBTM_A5

A24

Data Bit 5

ZBTM_D5

A5

Address Bit 6

ZBTM_A6

A23

Data Bit 6

ZBTM_D6

A4

Address Bit 7

ZBTM_A7

B32

Data Bit 7

ZBTM_D7

B12

Address Bit 8

ZBTM_A8

B31

Data Bit 8

ZBTM_D8

B11

Address Bit 9

ZBTM_A9

B30

Data Bit 9

ZBTM_D9

B10

Address Bit 10

ZBTM_A10

B28

Data Bit 10

ZBTM_D10

B9

Address Bit 11

ZBTM_A11

B29

Data Bit 11

ZBTM_D11

B8

Address Bit 12

ZBTM_A12

B27

Data Bit 12

ZBTM_D12

B7

Address Bit 13

ZBTM_A13

B24

Data Bit 13

ZBTM_D13

B6

Address Bit 14

ZBTM_A14

B23

Data Bit 14

ZBTM_D14

B5

Address Bit 15

ZBTM_A15

B22

Data Bit 15

ZBTM_D15

B4

Address Bit 16

ZBTM_A16

B21

Data Bit 16

ZBTM_D16

B3

Address Bit 17

ZBTM_A17

C33

Data Bit 17

ZBTM_D17

C2

Address Bit 18

ZBTM_A18

C28

RAM ReDA / Write

ZBTM_RW

B13

Address Bit 19

ZBTM_A19

C27

RAM Byte Write

Enable 1

ZBTM_BW1

D18

RAM Clock

ZBTM_CLK

B14

RAM Byte Write

Enable 2

ZBTM_BW2

D19

RAM Clock

Enable

ZBTM_CEN

C19

RAM Linear Burst

Order

ZBTM_LBO

D6

RAM Chip

Enable 0

ZBTM_CE0

C18

RAM Internal

Register LoDA

ZBTM_ALD

D8

RAM Chip

Enable 1

ZBTM_CE1

F19

RAM Output Enable

ZBTM_OE

C6

RAM Chip

Enable 2

ZBTM_CE2

E18

RAM Chip Enable 3

ZBTM_CE3

E19

11.1.1

DPX FPGA (U16) ZBT RAM Pin Configuration Table

11.2

DPX FPGA LED Configuration.

The DP Virtex-II FPGA has 10 amber LEDs for general purpose use.

Signal

LED

DP FPGA Pin No.

DPXLED0 D31

K21

DPXLED1 D32

K20

DPXLED2 D33

C22

DPXLED3 D34

C23

DPXLED4 D35

E21

DPXLED5 D36

E22

DPXLED6 D37

H21

DPXLED7 D38

H20

DPXLED8 D39

G20

DPXLED9 D40

F20

11.2.1

DPX FPGA (U16) LED Configuration Table