GV-395 Virtex-II DSP Hardware Accelerator Manual

GV & Associates, Inc.

07/10/04

30

13.0

Optional Daughter I/O PCBs for Analog Control FPGA (U14)

Descriptions

13.1

GVA-AD9430 170 MSPS 12 Bit A/D

The analog input is injected via a 50-ohm SMA connector (P1). The analog input voltage should not exceed 1.5 Vp-

p. The input Analog – Digital Converter (AD9430) is protected against accidental application of an over-voltage

input up to 3.8 Vp-p by a protection diodes. The analog signals are each sampled by a 100 MSPS analog to digital

converter (AD9432). The input sample clock (AD0_CLK) can be set to a maximum frequency of 170 MHz via the

Analog Control FPGA (U14). The sample clock may be generated either the 50 MHz system clock or from the

External Clock Input (P6). The LVTTL clock signal is coupled with a differential receiver (MC10EL16). The output

of this differential receiver drive the and ENC_CLK- inputs of the converter and provides the sub-

nanosecond rise times for optimum performance.

13.1.1

AC Coupled Analog Input Path

The analog input is AC coupled into two Mini-Circuits T1:1 transformer, which has a high pass corner at 50 KHz.

These transformers are used to generate a differential input to the AD9430.

13.1.2

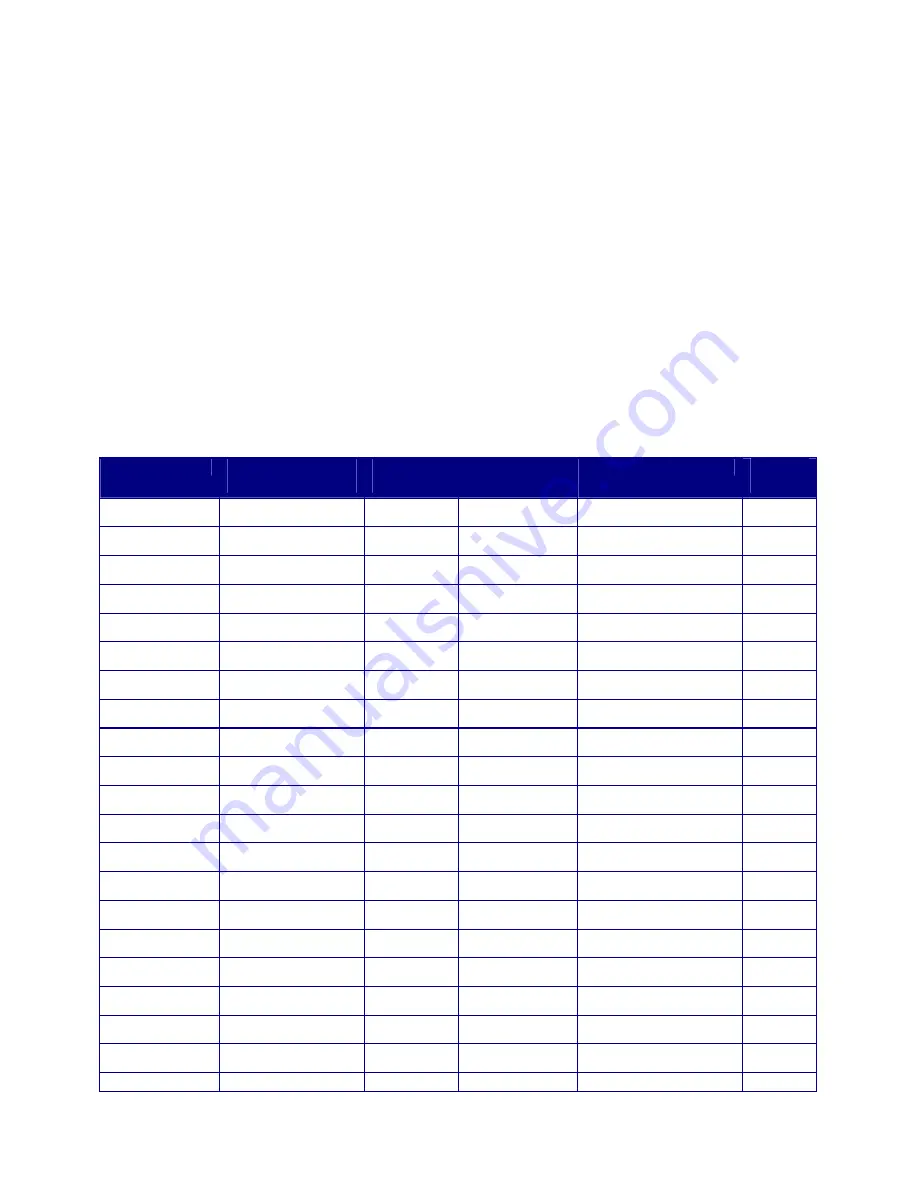

GVA-AD9430 Output Configuration

Signal Name

Signal Description

PC Pin

No.

Signal Name

Signal Description

PC Pin

No.

D11-

LVDS Output Data

Bit 11 Complement

1 D1+

LVDS Output Data

Bit 1

22

D11+

LVDS Output Data

Bit 11

2 D0-

LVDS Output Data

Bit 0 Complement

23

D10-

LVDS Output Data

Bit 10 Complement

3 D0+

LVDS Output Data

Bit 0

24

D10+

LVDS Output Data

Bit 10

4 AD_CLK-

LVDS Input

Clock Complement

25

D9-

LVDS Output Data

Bit 9 Complement

5 AD_CLK

LVDS Input

Clock

26

D9+

LVDS Output Data

Bit 9

6

+3.3V

+3.3 VDC Input

27

D8-

LVDS Output Data

Bit 8 Complement

7

+5V

+5 VDC Input

28

D8+

LVDS Output Data

Bit 8

8

+3.3V

+3.3 VDC Input

29

D7-

LVDS Output Data

Bit 7 Complement

9

+5V

+5 VDC Input

30

D7+

LVDS Output Data

Bit 7

10 DCO-

LVDS Output (JP5)

Data Clock Complement

31

D6-

LVDS Output Data

Bit 6 Complement

11 DCO+

LVDS Output (JP6)

Data Clock

32

D6+

LVDS Output Data

Bit 6

12 OR-

LVDS Output Data (JP7)

Over Range Complement

33

D5-

LVDS Output Data

Bit 5 Complement

13 OR+

LVDS Output Data (JP8)

Over Range

34

D5+

LVDS Output Data

Bit 5

14

TP5

Test Point 5

35

D4-

LVDS Output Data

Bit 4 Complement

15

TP8

Test Point 8

36

D4+

LVDS Output Data

Bit 4

16

TP6

Test Point 6

37

D3-

LVDS Output Data

Bit 3 Complement

17

TP7

Test Point 7

38

D3+

LVDS Output Data

Bit 3

18 DGND Digital

Ground

39

D2-

LVDS Output Data

Bit 2 Complement

19 DGND Digital

Ground

40

D2+

LVDS Output Data

Bit 2

20 DGND Digital

Ground

41

D1-

LVDS Output Data

21 DGND Digital

Ground

42