GV-395 Virtex-II DSP Hardware Accelerator Manual

GV & Associates, Inc.

07/10/04

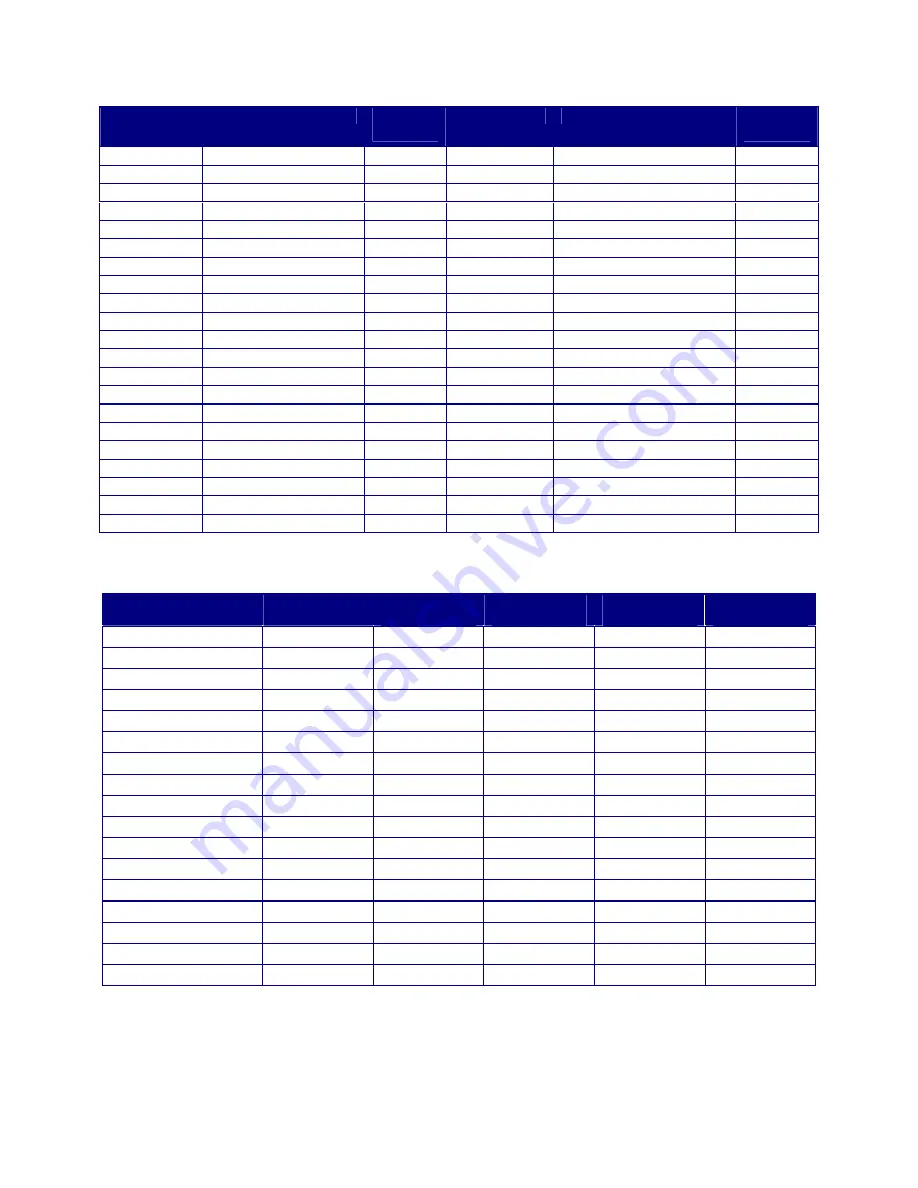

37

Signal Name

Signal Description

PC Pin

No.

Signal Name

Signal Description

PC Pin

No.

AD_OVR AD

Overflow

Bit 1

AD13

AD Output Bit 13

2

AD_DRY

AD Output Data Ready

3

AD11

AD Output Bit 11

4

AD_CLK

AD Input Sample Clock

25

AD12

AD Output Bit 12

5

26

AD9

AD Output Bit 9

6

+3.3V

+3.3 VDC Input

27

AD10

AD Output Bit 10

7

+5V

+5 VDC Input

28

AD7

AD Output Bit 7

8

+3.3V

+3.3 VDC Input

29

AD8

AD Output Bit 8

9

+5V

+5 VDC Input

30

AD5

AD Output Bit 5

10

AD0_OR

AD Overflow Bit

31

AD6

AD Output Bit 6

11

D_BUS1

DAughter PC DAta Bus 1

32

AD3

AD Output Bit 3

12

D_BUS2

DAughter PC DAta Bus 2

33

AD4

AD Output Bit 4

13

D_BUS3

DAughter PC DAta Bus 3

34

AD1

AD Output Bit 1

14

D_BUS4

DAughter PC DAta Bus 4

35

AD2

AD Output Bit 2

15

D_BUS5

DAughter PC DAta Bus 5

36

16

D_BUS6

DAughter PC DAta Bus 6

37

AD0

AD Output Bit 0

17

D_BUS7

DAughter PC DAta Bus 7

38

18

DGND

Digital

Ground

39

19

DGND

Digital

Ground

40

20

DGND

Digital

Ground

41

21

DGND

Digital

Ground

42

13.3.3.2

GVA-DA6645 to GVA-395 Interface Table

Signal Name

PC Pin No.

AC FPGA

PC #2 Pin No.

AC FPGA

PC #3 Pin No.

AC FPGA

PC #4 Pin No.

AC FPGA

PC #5 Pin No.

AD_D0 17

J1

N6 AB6 AH6

AD_D1 14

E4

N3 AD3 AL2

AD_D2 15

F5

P5 AC4 AL1

AD_D3 12

F3

M4 AD2 AJ3

AD_D4 13

F4

P3 AC3 AK2

AD_D5 10

F2

N2 AC1 AJ2

AD_D6 11

G3

N4 AC2 AH3

AD_D7 8

F1

K4 AB5 AJ1

AD_D8 9

G2

P2 AD1 AH2

AD_D9 6

D3

L3 AB4 AG3

AD_D10 7

G1

L4 AA5 AH1

AD_D11 4

D2

L2 AB2 AG2

AD_D12 5

E3

M3 AA4 AF3

AD_D13 2

D1

L1 AB1 AF1

AD_OVR 1 E1

M1 AA1 AE2

AD_DRY 3 E2

M2 AA2 AF2

AD_CLK 25 U1

U3 V1 W3

13.3.3.3

GVA-AD6645 to GVA-395 AC FPGA PC No. 2-5 Connection Table