FA1, FSCDIN — Host Address Bit One or SPI Serial Control Data Input

In parallel host mode, this pin serves as one of two address input pins used to select one of

four parallel registers. In SPI serial host mode, this pin serves as the data input.

INPUT

FHS1, FRD, FR/W — Mode Select Bit 1 or Host Parallel Output Enable or Host Parallel R/W

DSPAB control port mode select bit 1. This bit is one of 3 control port select bits that are

sampled on the rising edge of RESET to determine the control port mode of DSPAB. In Intel

parallel host mode, this pin serves as the active-low data bus enable input. In Motorola parallel

host mode, this pin serves as the read-high/write-low control input signal. In serial host mode,

this pin can serve as the external memory active-low data-enable output signal.

BIDIRECTIONAL - Default: INPUT

FHS0, FWR, FDS — Mode Select Bit 0 or Host Write Strobe or Host Data Strobe

DSPAB control port mode select bit 0. This bit is one of 3 control port select bits that are

sampled on the rising edge of RESET to determine the control port mode of DSPAB. In Intel

parallel host mode, this pin serves as the active-low data-write-input strobe. In Motorola

parallel host mode, this pin serves as the active-low data-strobe-input signal. In serial host

mode, this pin can serve as the external-memory active-low write-enable output signal.

BIDIRECTIONAL - Default: INPUT

FCS — Host Parallel Chip Select, Host Serial SPI Chip Select

In parallel host mode, this pin serves as the active-low chip-select input signal. In serial host

SPI mode, this pin is used as the active-low chip-select input signal.

INPUT

FHS2, FSCDIO, FSCDOUT — Mode Select Bit 2 or Serial Control Port Data Input and Output, Par-

allel Port Type Select

DSPAB control port mode select bit 2. This bit is one of 3 control port select bits that are

sampled on the rising edge of RESET to determine the control port mode of DSPAB. In SPI

mode this pin serves as the data output pin. In parallel host mode, this pin is sampled at the

rising edge of RESET to configure the parallel host mode as an Intel type bus or as a

Motorola type bus.

BIDIRECTIONAL - Default: INPUT

FINTREQ — Control Port Interrupt Request

Open-drain interrupt-request output. This pin is driven low to indicate that the DSP has

outgoing control data that should be read by the host.

OPEN DRAIN I/O - Requires 3.3K Ohm Pull-Up

FSCLKN1, STCCLK2

—

PCM Audio Input Bit Clock

Digital-audio bit clock input. FSCLKN1 operates asynchronously from all other DSPAB clocks.

In master mode, FSCLKN1 is derived from DSPAB

’s

internal clock generator. The active edge

of FSCLKN1 can be programmed by the DSP.

BIDIRECTIONAL - Default: INPUT

FLRCLKN1 — PCM Audio Input Sample Rate Clock

AVR340

harman/kardon

113

Summary of Contents for AVR 340

Page 33: ...AVR340 harman kardon 33...

Page 35: ...AVR340 harman kardon 35...

Page 80: ...AVR340 harman kardon...

Page 81: ...AVR340 harman kardon...

Page 82: ...AVR340 harman kardon 82...

Page 83: ...CAM350 PRO V 7 6 Mon Sep 01 10 29 56 2003 Untitled AVR340 harman kardon 83...

Page 84: ...AVR340 harman kardon 84...

Page 85: ...AVR340 harman kardon 85...

Page 123: ...AVR340 harman kardon 123...

Page 124: ...AVR340 harman kardon 124...

Page 125: ...AVR340 harman kardon 125...

Page 126: ...AVR340 harman kardon 126...

Page 129: ...AVR340 harman kardon 129...

Page 130: ...AVR340 harman kardon 130...

Page 131: ...AVR340 harman kardon 131...

Page 132: ...AVR340 harman kardon 132...

Page 133: ...AVR340 harman kardon 133...

Page 134: ...AVR340 harman kardon 134...

Page 135: ...AVR340 harman kardon 135...

Page 136: ...AVR340 harman kardon 136...

Page 137: ...AVR340 harman kardon 137...

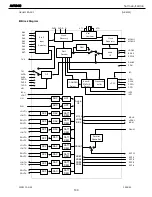

Page 139: ...TC90A49P F BLOCK DIAGRAM PIN ASSIGNMENT AVR340 harman kardon 139...

Page 148: ...AVR340 harman kardon 148...

Page 151: ...LC74763M BLOCK DIAGRAM AVR340 harman kardon 151...

Page 158: ...AVR340 harman kardon 158...

Page 159: ...AVR340 harman kardon 159...

Page 162: ...AVR340 harman kardon 162...

Page 166: ...AVR340 harman kardon 166...

Page 167: ...AVR340 harman kardon 167...

Page 168: ...AVR340 harman kardon 168...

Page 169: ...AVR340 harman kardon 169...

Page 170: ...AVR340 harman kardon 170...

Page 171: ...AVR340 harman kardon 171...

Page 172: ...AVR340 harman kardon 172...

Page 173: ...AVR340 harman kardon 173...

Page 176: ...AVR340 harman kardon 176...

Page 178: ...AVR340 harman kardon 178...

Page 179: ...SCHEMATIC sch 1 Fri Oct 21 10 53 55 2005 AVR340 harman kardon 179...

Page 180: ...LPP 051021 sch 1 Fri Oct 21 10 40 28 2005 AVR340 harman kardon 180...

Page 181: ...NPUT LPP 051021 sch 2 Fri Oct 21 10 42 09 2005 AVR340 harman kardon 181...

Page 182: ...UT LPP 051021 sch 3 Fri Oct 21 10 43 03 2005 AVR340 harman kardon 182...

Page 183: ...EMATIC sch 1 Fri Oct 21 10 52 43 2005 AVR340 harman kardon 183...

Page 184: ...CHEMATIC sch 1 Fri Oct 21 10 56 51 2005 AVR340 harman kardon 184...

Page 185: ...SCHEMATIC sch 2 Thu Oct 27 15 39 31 2005 AVR340 harman kardon 185...

Page 186: ..._0810 sch 1 Wed Aug 10 16 28 25 2005 AVR340 harman kardon 186...