APEX

™

Exciter Incorporating FLO

™

Technology

Navigating the LCD Display Screens

Details of the System Setup Screens

Page: 3-48

888-2604-001

03/08/07

WARNING: Disconnect primary power prior to servicing.

3.6.7

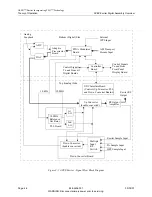

FPGA Setup

The FPGA modulator setup is accomplished in the following nine screens.

3.6.7.1

FPGA Configure 1/5

FPGASetup1.bmp

Figure 3-40 FPGA Configure 1/5

FPGA Configure 1/5 consists of registers whose values are written immediately to the

FPGA when changed through the GUI.

No FPGA re-initialization occurs when any of these registers are changed.

The parameters of the FPGA Configure 1/5 screen are as follows.

•

Transmitter ID:

(Unsigned 16-bit Decimal, range 0 to 65535)

•

Wide Area PID:

(Unsigned 13-bit Decimal, range 0 to 8191)

•

Local Area PID:

(Unsigned 13-bit Decimal, range 0 to 8191)

•

TS Stream Control:

(TS1 Active/TS2 Active)

•

TS Source Control:

(Automatic/Manual)

•

Infrastructure ID:

(Unsigned 16-bit Decimal, range 0 to 65535)

•

Local Time Offset:

(Signed Real Decimal in Hours, range -16.0 to +15.5 in 0.5 in-

crements

Register value is calculated as [Local Time Offset]*2)

•

Daylight Savings:

(Standard/Daylight)