Device Connections and Switches

96/145

PC Cards cifX PCI, PCIe, Low Profile PCIe | Installation, Operation and Hardware Description

DOC120204UM36EN | Revision 36 | English | 2012-10 | Released | Public

© Hilscher, 2008-2012

9.10.3

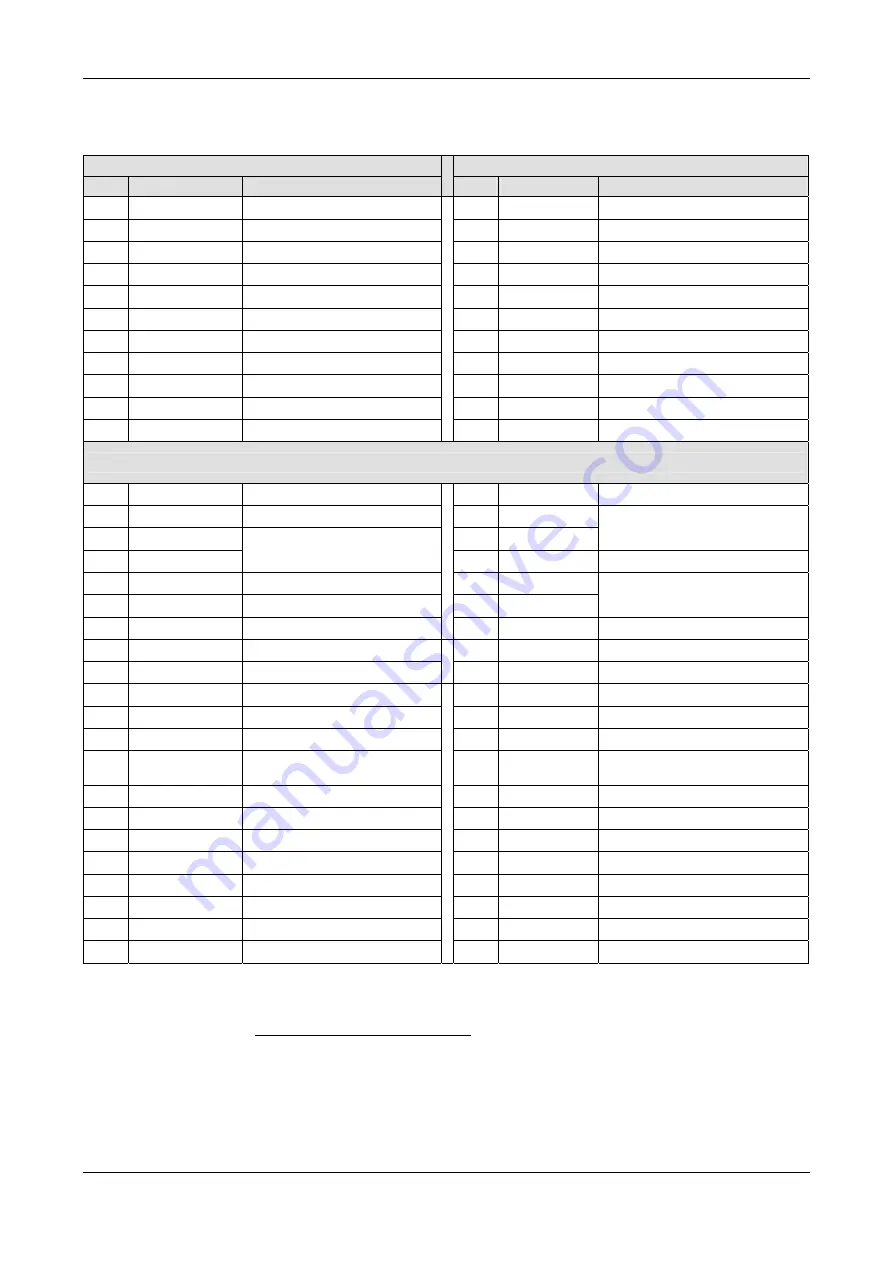

Pin Assignment for PCI Express Bus CIFX 100EH-RE\CUBE

Only for: CIFX 100EH-RE\CUBE (x1 = One Lane)

4

PCI Express Bus X2 (Side B)

PCI Express Bus X1 (Side A)

Pin

Name

Description

Pin

Name

Description

B1

n. u.

(not used)

A1

PRSNT1#

Hot-Plug presence detect

B2

n. u.

(not used)

A2

n. u.

(not used)

B3

n. u.

(not used)

A3

n. u.

(not used)

B4 GND

Ground

A4 GND

Ground

B5

n. u.

(not used)

A5 JTAG-TCK JTAG

Test

Clock

B6

n. u.

(not used)

A6

JTAG-TDI

JTAG Test Data Input

B7 GND

Ground

A7 JTAG-TDO JTAG Test Data Output

B8 3V3

3,3V

Power

A8 JTAG-TMS

JTAG Test Mode Select Input

B9

JTAG-TRST#

JTAG Test Reset

A9

3V3

3,3V Power

B10

n. v.

(not used)

A10 3V3

3,3V

Power

B11

n. u.

(not used)

A11 PERST#

PCIe

Reset

Key

B12

n. u.

(not used)

A12 GND

Ground

B13 GND

Ground

A13 P

B14 PCIe_TP

A14 PCIe_CLK-

PCIe Clock

differential pair

B15 PCIe_TN

Transmitter Lane,

differential pair

A15 GND

Ground

B16 GND

Ground

A16 PCIe_RP

B17

PRSNT2#

Hot-Plug presence detect

A17

PCIe_RN

Receiver Lane,

differential pair

B18 GND

Ground

A18 GND

Ground

B19

n. u.

(not used)

A19

n. u.

(not used)

B20

n. u.

(not used)

A20

n. u.

(not used)

B21

n. u.

(not used)

A21

n. u.

(not used)

B22

n. u.

(not used)

A22

n. u.

(not used)

B23 GND

Ground

A23

n. u.

(not used)

B24

IO_SYNC0 /

IO_SYNC1 / 3,3V

5

Real-Time Ethernet SYNC

6

A24

n. u.

(not used)

B25 GND

Ground

A25

n. u.

(not used)

B26

SPI_CS#

ID Chip Select

A26

n. u.

(not used)

B27

SPI_MOSI

ID Slave In

A27

n. u.

(not used)

B28

SPI_MISO

ID Slave Out

A28

n. u.

(not used)

B29 SPI_CLK

ID

Clock

A29

n. u.

(not used)

B30 GND

Ground

A30

n. u.

(not used)

B31

n. u.

(not used)

A31

n. u.

(not used)

B32

n. u.

(not used)

A32

n. u.

(not used)

Table 86: Pin Assignment for PCI Express-Bus CIFX 100EH-RE\CUBE

4

Pinning A19 to A32 / B19 to B32 not standard conform [bus spec 3, page 73-74].

5

If at the SYNC connector J3 the jumper is set, the IO_SYNC signal is transferred

to the PCI Express Bus X2 pin B24 (jumper on pin1-pin2(J3):

IO_SYNC0

, pin2-

pin3(J3):

IO_SYNC1

). If no jumper is set, the signal is

3,3V

static High

(with Pull-up)

.

Refer to section

Pin Assignment SYNC Connector, J3

, on page 93.

6

in 3V3 logic.