5K250 (SATA) OEM Specification

Page 114 of 171

14.19

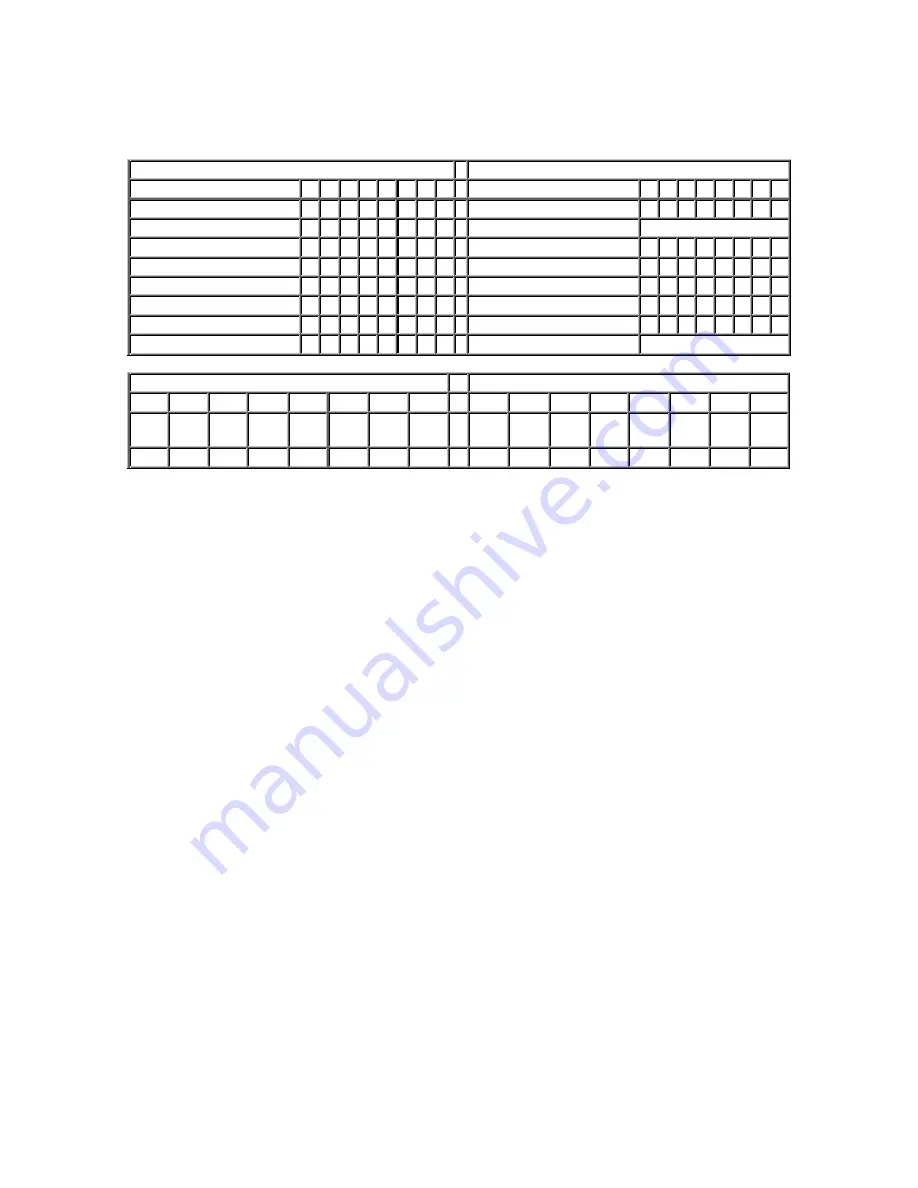

Read Native Max Address (F8h)

Block Output Registers Command

Command Block Input Registers

Register

7 6 5 4 3 2 1 0

Register

7 6 5 4 3 2 1 0

Data

-

-

-

-

-

-

-

-

Data

-

-

-

-

-

-

-

-

Feature

-

-

-

-

-

-

-

-

Error

...See Below...

Sector Count

-

-

-

-

-

-

-

-

Sector Count

-

-

-

-

-

-

-

-

LBA Low

-

-

-

-

-

-

-

-

LBA Low

V V V V V V V V

LBA Mid

-

-

-

-

-

-

-

-

LBA Mid

V V V V V V V V

LBA High

-

-

-

-

-

-

-

-

LBA High

V V V V V V V V

Device

- L -

-

-

-

-

-

Device

-

-

-

- H H H H

Command

1 1 1 1 1 0 0 0

Status

...See Below...

Error Register

Status Register

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0

CRC UNC 0

IDN

0 ABT T0N

AM

N

BSY RDY

DF

DSC DRQ

COR IDX

ERR

0 0 0 0 0 V 0 0

0 V 0 - - 0 0 V

Table 85 Read Native Max Address Command (F8h)

This command returns the native max LBA/CYL of HDD which is not affected by Set Max Address

command.

The 48-bit native max address is greater than 268,435,455, the Read Native Max Address command

return a value of 268,435,455.

Output Parameters To The Device

L

LBA mode.Indicates the addressing mode.L=0 specifies CHS mode and L=1 does LBA

addressing mode.

D

The device number bit. Indicates that the device number bit of the Device Register

should be specified. D=0 selects the master device and D=1 selects the slave device.

-

Indicates that the bit is not used.

Input Parameters From The Device

LBA Low

In LBA mode, this register contains native max LBA bits 0 - 7. (L=1)

In CHS mode, this register contains native max LBA Low. (L=0)

LBA

High/Mid

In LBA mode, this register contains native max LBA bits 8 - 15 (Mid), 16 - 23 (High).

(L=1)

In CHS mode, this register contains native max cylinder number. (L=0)

H

In LBA mode, this register contains native max LBA bits 24 - 27. (L=1)

In CHS mode, this register contains native max head number.(L=0)

V

Valid. Indicates that the bit is part of an input parameter and will be set to 0 or 1 by the

device.

-

Indicates that the bit is not used.