33

1–3,6–11,

53–60

Delay RAM

Address

Generating

Circuit

5,14,34,52

17–15

42–44

Data RAM

128w

×

24b

Program

ROM

1024w

×

32b

Multiply

and add

Culculator

24b

×

16b+43b

Delay RAM

4096w

×

16b

Offset RAM

64w

×

16b

Coefficient

RAM

320w

×

16b

Coefficient

ROM

256w

×

16b

Program

Counter

Logical

Arithmetic

Unit(LU)

Work

Register

Temporary

Register

Interface

Circuit

Serial Data

Input/Output

Circuit

Input (2 port)

Output (3 port)

Timing

Generation

Circuit

VCO Oscillation

Circuit

32

33

27

24

Interface bus

Data bus

Work register

bus

ELRI1,ELRI0

EBCI1,EBCI0

45

13 12

30

36

35

20

21

22

23

40

37

41

49 51

48

50

47

46

39 38

28,29

25,26

4,31

18,19

CS

IFCD

IFCK

IFDI

IFDO

ACK

SDI1

SDI0

SDO0

SDO2

VDDA

PD

AMPI

A

MPO

VSSA

CKSL

PLOFF

XI

XO

SYNC

ELRO

EBCO

LR

WCK

FS32

FS64

VDDR

RST

TES0

TES2

TPS0

TPS16

VSSR

VDD

VSS

24b

16b

.

o

N

e

m

a

N

n

i

P

O

/

I

n

o

i

t

c

n

u

F

1

8

P

T

O

n

i

p

t

u

p

t

u

o

a

t

a

d

t

s

e

T

.

n

e

p

o

h

t

i

w

e

s

u

,

y

ll

a

m

r

o

N

2

7

P

T

3

6

P

T

4

D

D

V

−

n

i

p

y

l

p

p

u

s

r

e

w

o

P

5

S

S

V

−

n

i

p

d

n

u

o

r

G

6

5

P

T

O

n

i

p

t

u

p

t

u

o

a

t

a

d

t

s

e

T

.

n

e

p

o

h

t

i

w

e

s

u

,

y

ll

a

m

r

o

N

7

4

P

T

8

3

P

T

9

2

P

T

0

1

1

P

T

1

1

0

P

T

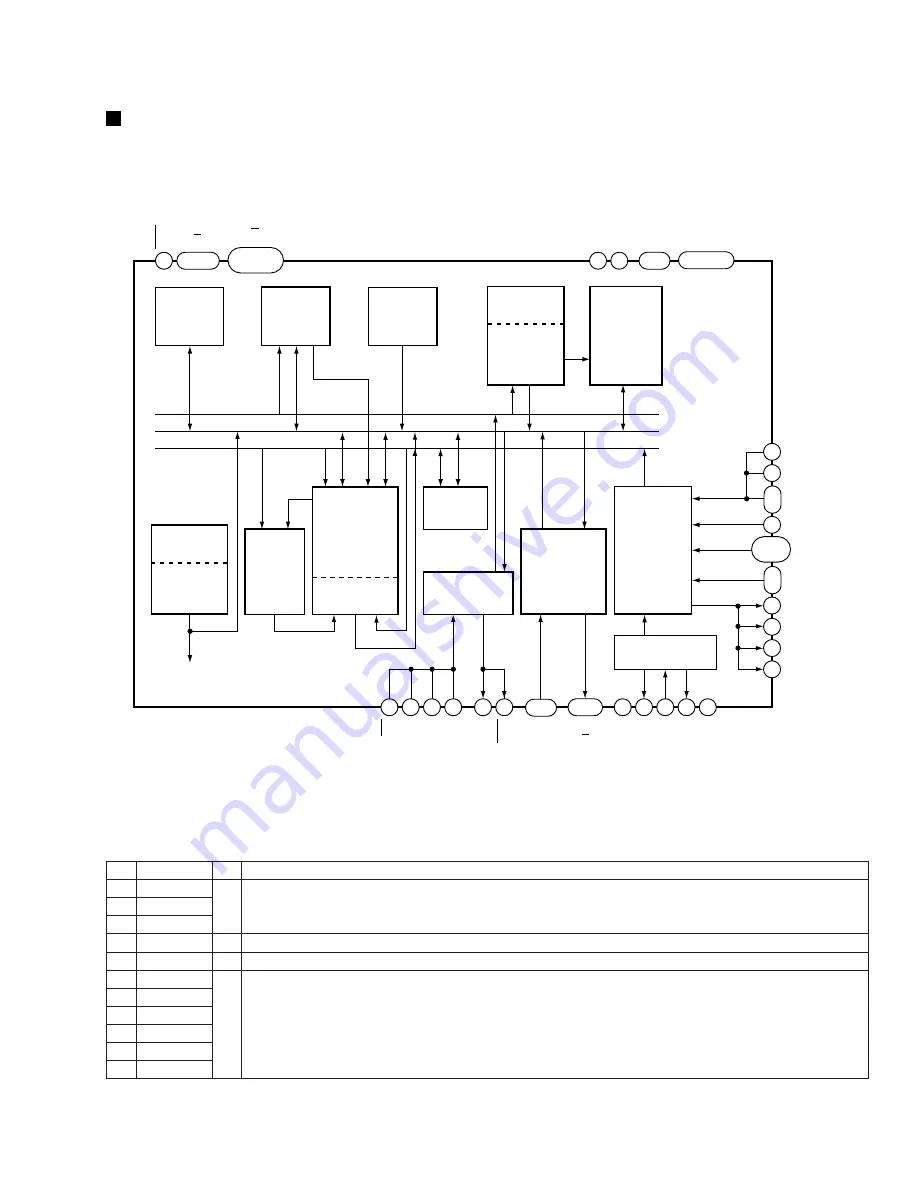

PD2058A ( DVDM ASSY : IC901 )

• Digital Signal Processor For Audio

•

Block Diagram

•

Pin Function