Chapter 8 Register Structure

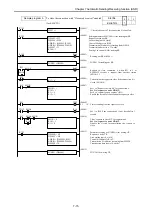

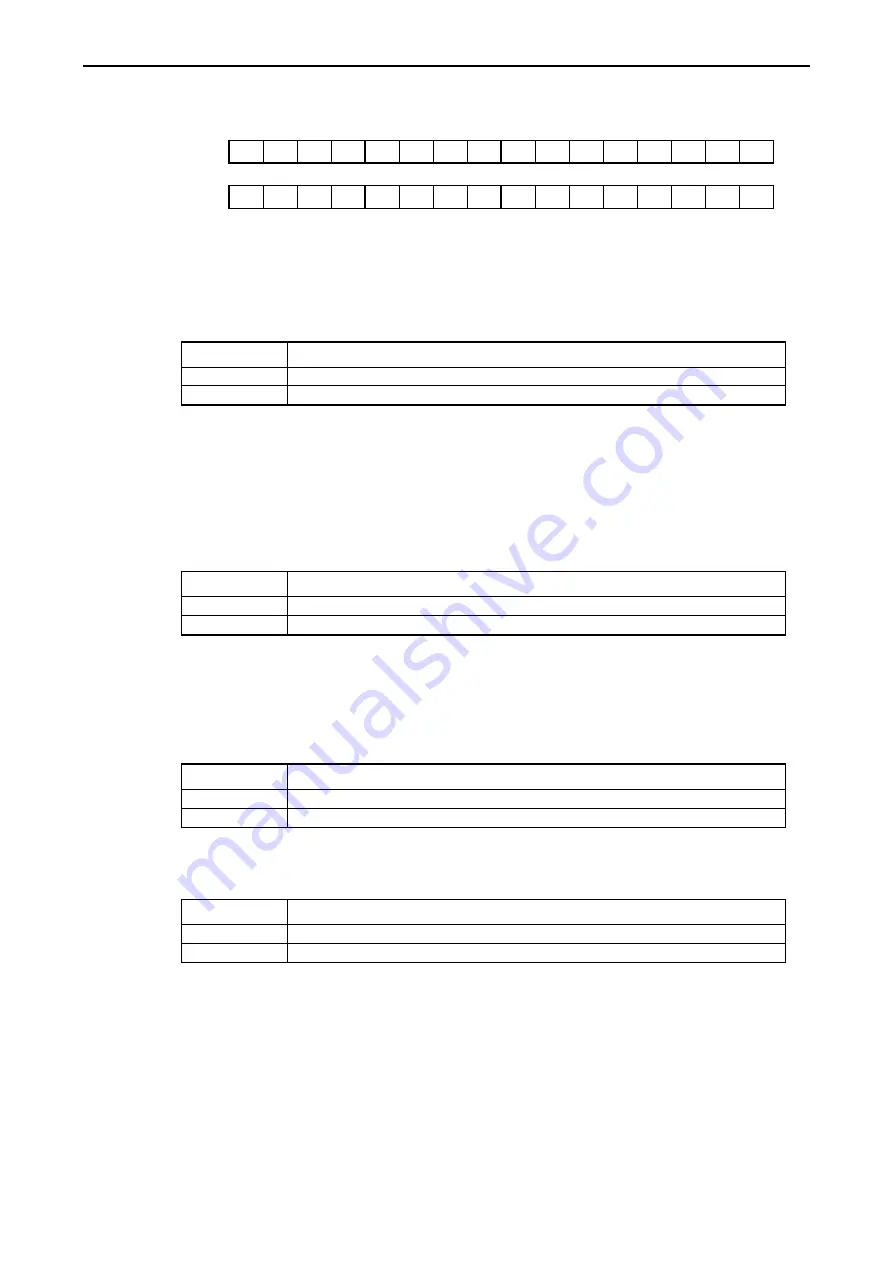

Connection n error status register (CnESR) n = 1 to 6

Bit

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

+H1

- - - - - - - - -

ATE1 SNE1 RCE1

RAE1

- STE1

OE1

:

+H6

- - - - - - - - -

ATE6 SNE6 RCE6

RAE6

- STE6

OE6

The error condition of each connection (1 to 6) is shown in this area.

Bit 15-7: Reserved

These bits are reserved. Normally "0" is set.

Bit 6: ASR table set-up error bit (ATE[6:1])

These bits show the error condition of Automatic Sending/Receiving (ASR) table set-up.

Bit6: ATE[6:1]

Description

0

No error is detected in ASR table set-up.

1

An error is detected in ASR table set-up.

Method to clear : To clear these bits to "0", please set the correct ASR table again.

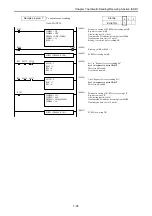

Bit 5: Send error bit (SNE[6:1])

These bits are set below condition.

-

At data send, there is a error of data transmission between EH-ETH2 and CPU module.

-

There is a request for sending data to EH-ETH2 before EH-ETH2 has not completed the previous data

sending process.

When “send data error” occurs, data in the sending area in CPU module is guaranteed, but data in the sending

buffer in EH-ETH2 and receiving data at other station are not guaranteed.

Bit5: SNE[6:1]

Description

0

No error is detected during the data sending.

1

An error is detected during the data sending.

Method to clear : To clear these bits to "0", please set "1" to SNC[6:1] of EC3CR.

Bit 4: Receive error bit (RCE[6:1])

These bits are set below condition.

-

At data receiving, there is a error of data transmission between EH-ETH2 and CPU module.

When receive error occurs, receiving area data in CPU module and receiving buffer data in EH-ETH2 and

receiving data at other station are not guaranteed.

Bit4: RCE[6:1]

Description

0

No error is detected during the data receiving.

1

An error is detected during the data receiving.

Method to clear: To clear these bits to "0", please set "1" to RCC[6:1] of EC3CR.

Bit 3: Receive area error bit (RAE[6:1])

These bits show the receiving data size is more than allowed size or not.

Bit3: RAE[6:1]

Description

0

Size of received data dose not exceed Receive area size.

1

Size of received data exceeds Receive area size.

Method to clear: To clear these bits to "0", please set "1" to RAC[6:1] of EC2CR.

Bit 2: Reserved

This bit is reserved. Normally "0" is set.

8-3