2.2.54 (1) SHAR (B)

SHAR (SHift Arithmetic Right)

Shift Arithmetic

Operation

Rd (right arithmetic shift)

→

Rd

Assembly-Language Format

SHAR.B

Rd

Operand Size

Byte

Condition Code

H: Previous value remains unchanged.

N: Set to 1 if the result is negative; otherwise

cleared to 0.

Z:

Set to 1 if the result is zero; otherwise

cleared to 0.

V: Set to 1 if an overflow occurs; otherwise

cleared to 0.

C: Receives the previous value in bit 0.

I

UI

H

U

N

Z

V

C

—

—

—

—

↕

↕

0

↕

Description

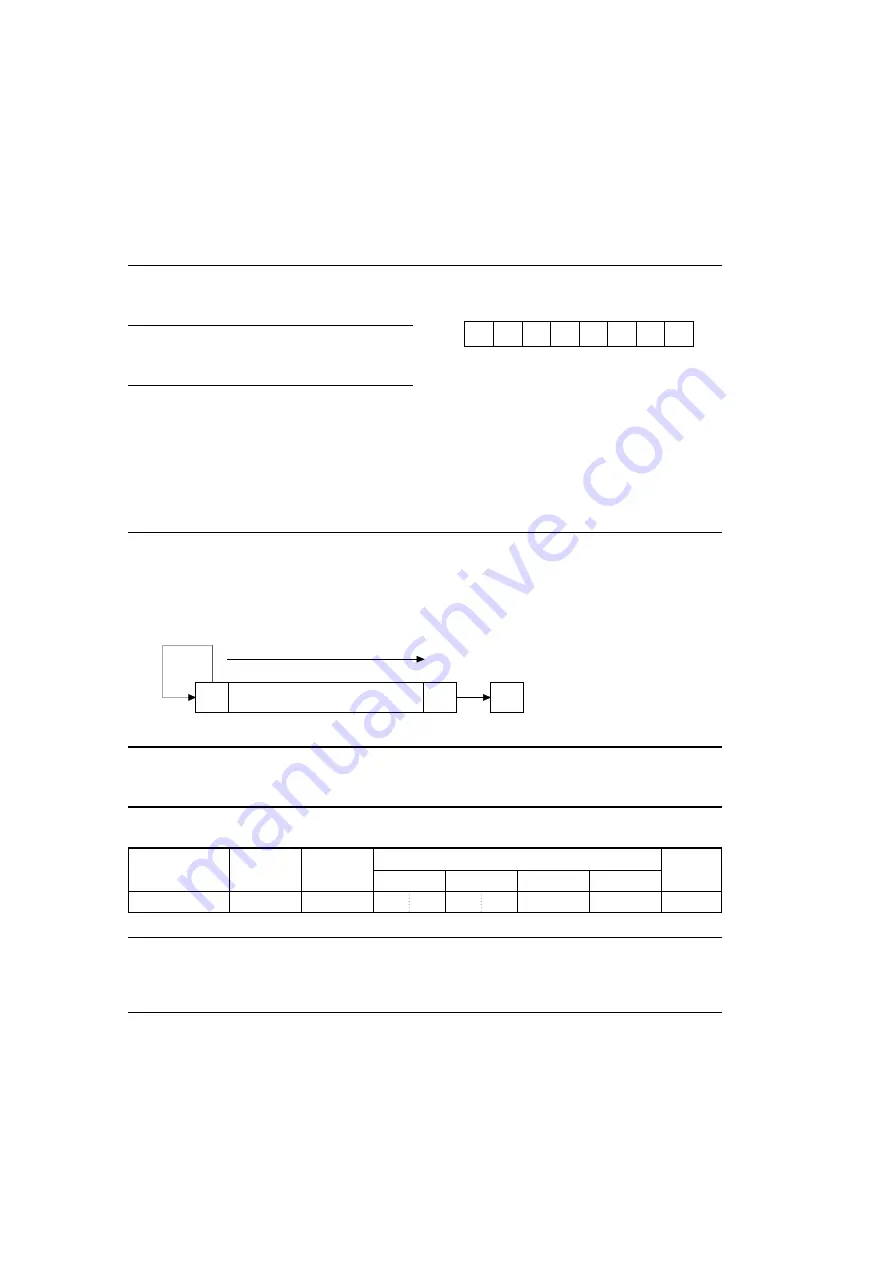

This instruction shifts the bits in an 8-bit register Rd (destination operand) one bit to the right. Bit

0 shifts into the carry flag. Bit 7 shifts into itself. Since bit 7 remains unaltered, the sign does not

change.

Available Registers

Rd: R0L to R7L, R0H to R7H

Operand Format and Number of States Required for Execution

Notes

LSB

b

7

b

0

. . . . . .

C

MSB

Instruction Format

1st byte

2nd byte

3rd byte

4th byte

Register direct

SHAR.B

Rd

1

1

8

rd

2

No. of

States

Addressing

Mode

Mnemonic

Operands

164