2.2.55 (1) SHLL (B)

SHLL (SHift Logical Left)

Shift Logical

Operation

Rd (left logical shift)

→

Rd

Assembly-Language Format

SHLL.B

Rd

Operand Size

Byte

Condition Code

H: Previous value remains unchanged.

N: Set to 1 if the result is negative; otherwise

cleared to 0.

Z:

Set to 1 if the result is zero; otherwise

cleared to 0.

V: Always cleared to 0.

C: Receives the previous value in bit 7.

I

UI

H

U

N

Z

V

C

—

—

—

—

↕

↕

0

—

Description

This instruction shifts the bits in an 8-bit register Rd (destination operand) one bit to the left. The

most significant bit shifts into the carry flag. The least significant bit (bit 0) is cleared to 0.

Available Registers

Rd: R0L to R7L, R0H to R7H

Operand Format and Number of States Required for Execution

Notes

The SHLL instruction differs from the SHAL instruction in its effect on the overflow flag.

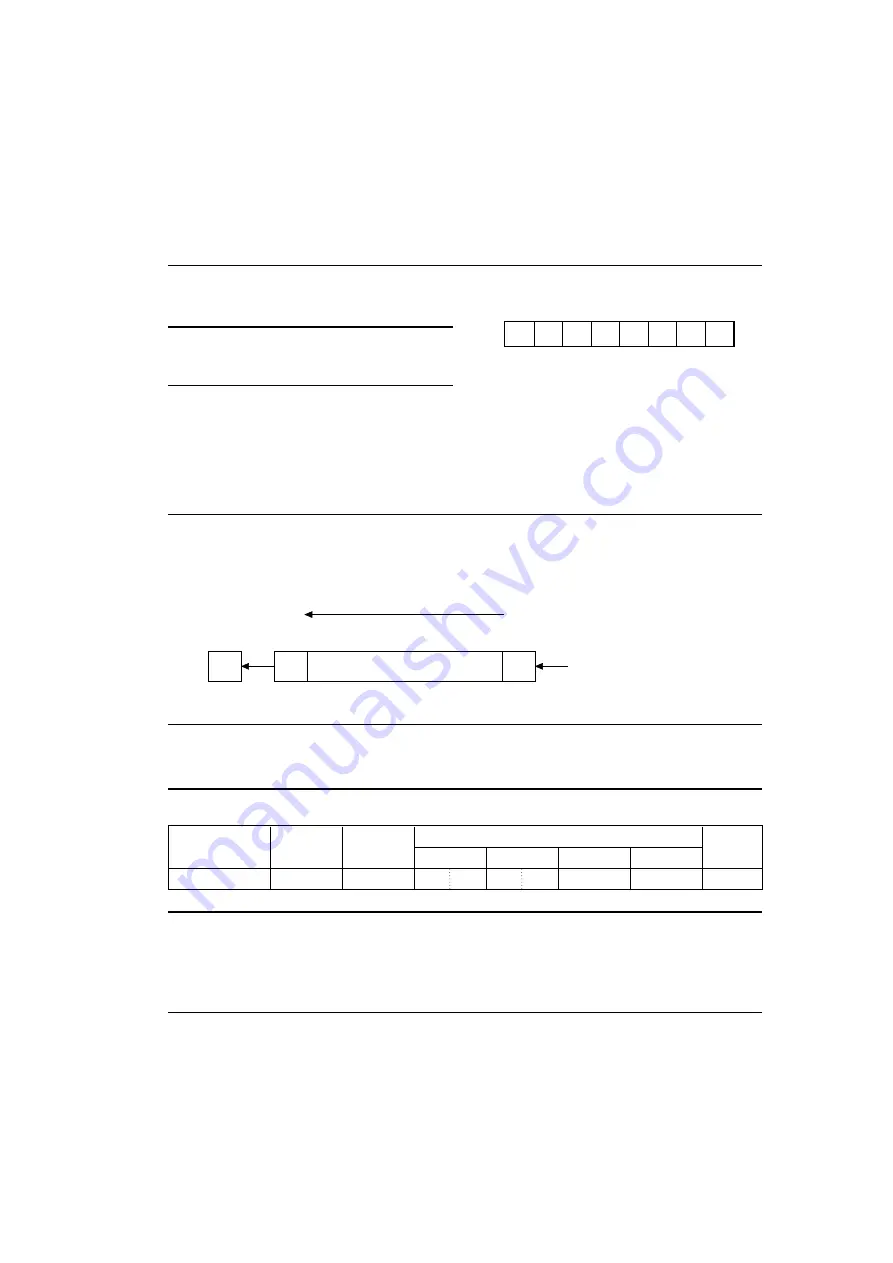

LSB

MSB

b

7

b

0

. . . . . .

C

0

Instruction Format

1st byte

2nd byte

3rd byte

4th byte

Register direct

SHLL.B

Rd

1

0

0

rd

2

No. of

States

Addressing

Mode

Mnemonic

Operands

167