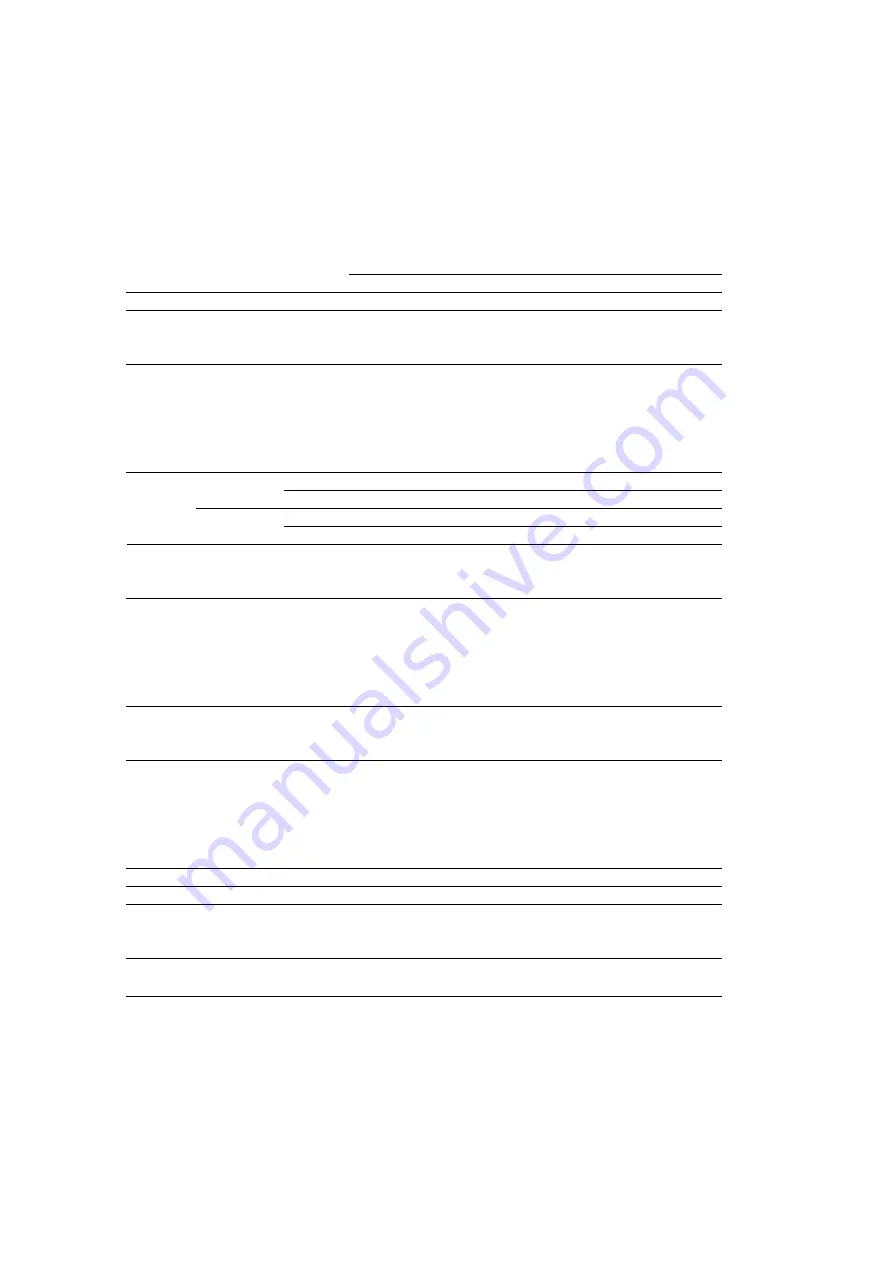

Table 2-8 Number of Cycles in Instruction Execution (cont)

Branch

Instruction

Address

Stack

Byte Data

Word Data Internal

Fetch

Read

Operation

Access

Access

Operation

Instruction

Mnemonic

I

J

K

L

M

N

BNOT

BNOT Rn,@aa:8

2

2

BOR

BOR #xx:3,Rd

1

BOR #xx:3,@ERd

2

1

BOR #xx:3,@aa:8

2

1

BSET

BSET #xx:3,Rd

1

BSET #xx:3,@ERd

2

2

BSET #xx:3,@aa:8

2

2

BSET Rn,Rd

1

BSET Rn,@ERd

2

2

BSET Rn,@aa:8

2

2

BSR

BSR d:8

Advanced

2

2

Normal

2

1

BSR d:16

Advanced

2

2

2

Normal

2

1

2

BST

BST #xx:3,Rd

1

BST #xx:3,@ERd

2

2

BST #xx:3,@aa:8

2

2

BTST

BTST #xx:3,Rd

1

BTST #xx:3,@ERd

2

1

BTST #xx:3,@aa:8

2

1

BTST Rn,Rd

1

BTST Rn,@ERd

2

1

BTST Rn,@aa:8

2

1

BXOR

BXOR #xx:3,Rd

1

BXOR #xx:3,@ERd

2

1

BXOR #xx:3,@aa:8

2

1

CMP

CMP.B #xx:8,Rd

1

CMP.B Rs,Rd

1

CMP.W #xx:16,Rd

2

CMP.W Rs,Rd

1

CMP.L #xx:32,ERd

3

CMP.L ERs,ERd

1

DAA

DAA Rd

1

DAS

DAS Rd

1

DEC

DEC.B Rd

1

DEC.W #1/2,Rd

1

DEC.L #1/2,ERd

1

DIVXS

DIVXS.B Rs,Rd

2

12

DIVXS.W Rs,ERd

2

20

216