3.3.2 Exception-Handling Sequences

Reset Exception Handling: Reset exception handling has the highest priority. The reset state is

entered when the RES signal goes low. Then, if RES goes high again, reset exception handling

starts when the reset condition is satisfied. Refer to the relevant microcontroller hardware manual

for details about the reset condition. When reset exception handling starts the CPU fetches a start

address from the exception vector table and starts program execution from that address. All

interrupts, including NMI, are disabled during the reset exception-handling sequence and

immediately after it ends.

Interrupt Exception Handling and Trap Instruction Exception Handling: When these

exception-handling sequences begin, the CPU references the stack pointer (ER7) and pushes the

program counter and condition-code register on the stack. Next, if the UE bit in the system control

register (SYSCR) is set to 1, the CPU sets the I bit in the condition-code register to 1. If the UE bit

is cleared to 0, the CPU sets both the I bit and the UI bit in the condition-code register to 1. Then

the CPU fetches a start address from the exception vector table and execution branches to that

address.

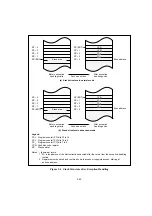

The program-counter value pushed on the stack and the start address fetched from the vector table

are 16 bits long in normal mode and 24 bits long in advanced mode. Figure 3-4 shows the stack

after the exception-handling sequence.

242