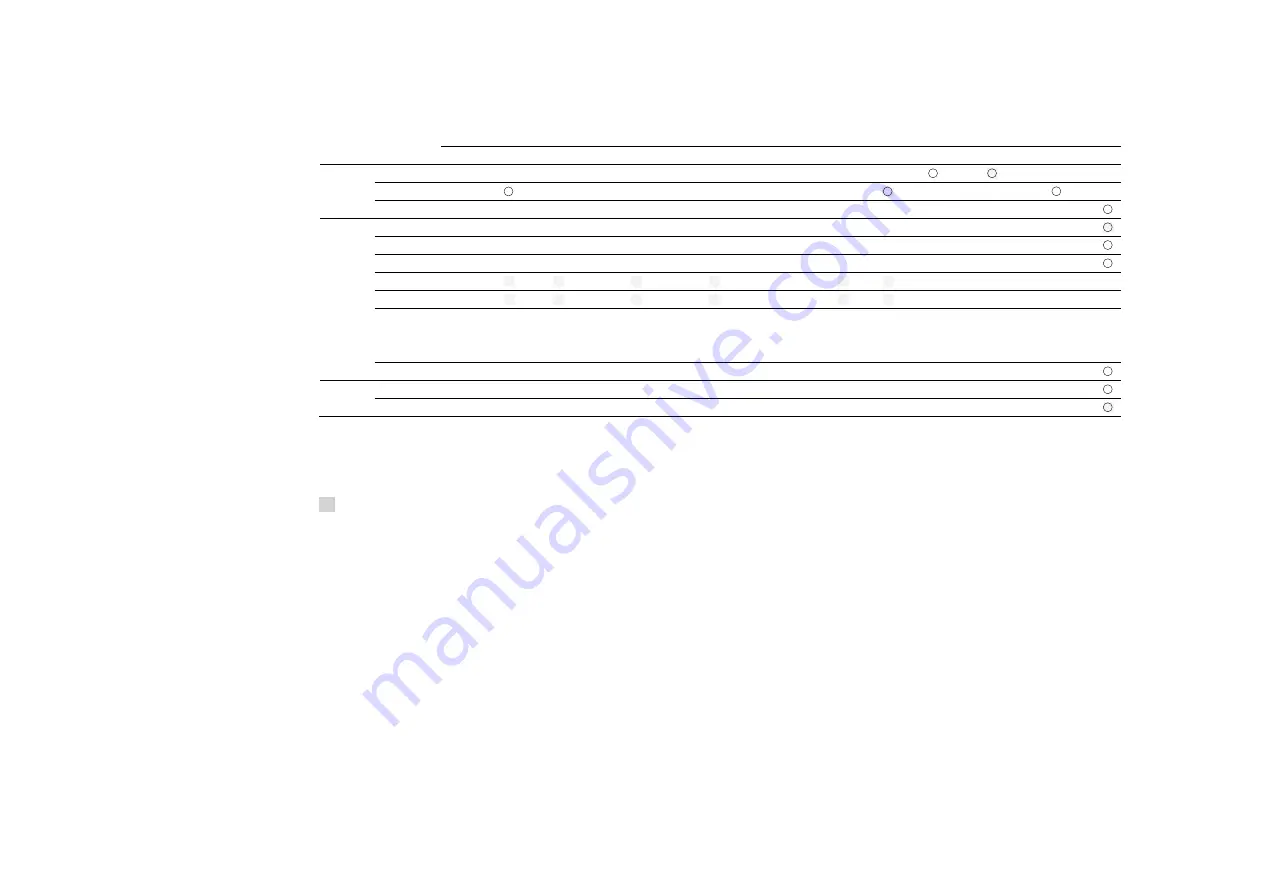

Table 1-2 Instruction Set Overview (cont)

Legend

B: Byte

W: Word

L: Longword

: Newly added instruction in H8/300H CPU

Notes: 1. The operand size of the ADDS and SUBS instructions of the H8/300H CPU has been changed to longword size. (In the

H8/300 CPU it was word size.)

2. Because of its larger address space, the H8/300H CPU uses a 24-bit absolute address for the JMP and JSR instructions.

(The H8/300 CPU used 16 bits.)

17

Addressing Modes

Function

Instruction

#xx

Rn

@ERn

@(d:16,ERn)

@(d:24,ERn)

@ERn+/@–ERn

@aa:8 @aa:16 @aa:24 @(d:8,PC) @(d:16,PC) @@aa:8

—

Bcc, BSR

JMP, JSR

RTS

TRAPA

RTE

SLEEP

LDC

STC

ANDC,

ORC,

XORC

NOP

EEPMOV.B

EEPMOV.W

Branch

System

control

Block data

transfer

*

2

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

B

—

B

—

—

—

—

—

—

—

—

—

B

B

—

—

—

—

—

—

—

—

—

W

W

—

—

—

—

—

—

—

—

—

—

W

W

—

—

—

—

—

—

—

—

—

—

W

W

—

—

—

—

—

—

—

—

—

—

W

W

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

W

W

—

—

—

—

—

—

—

—

—

W

W

—

—

—

—

—

—

—

—

—