137

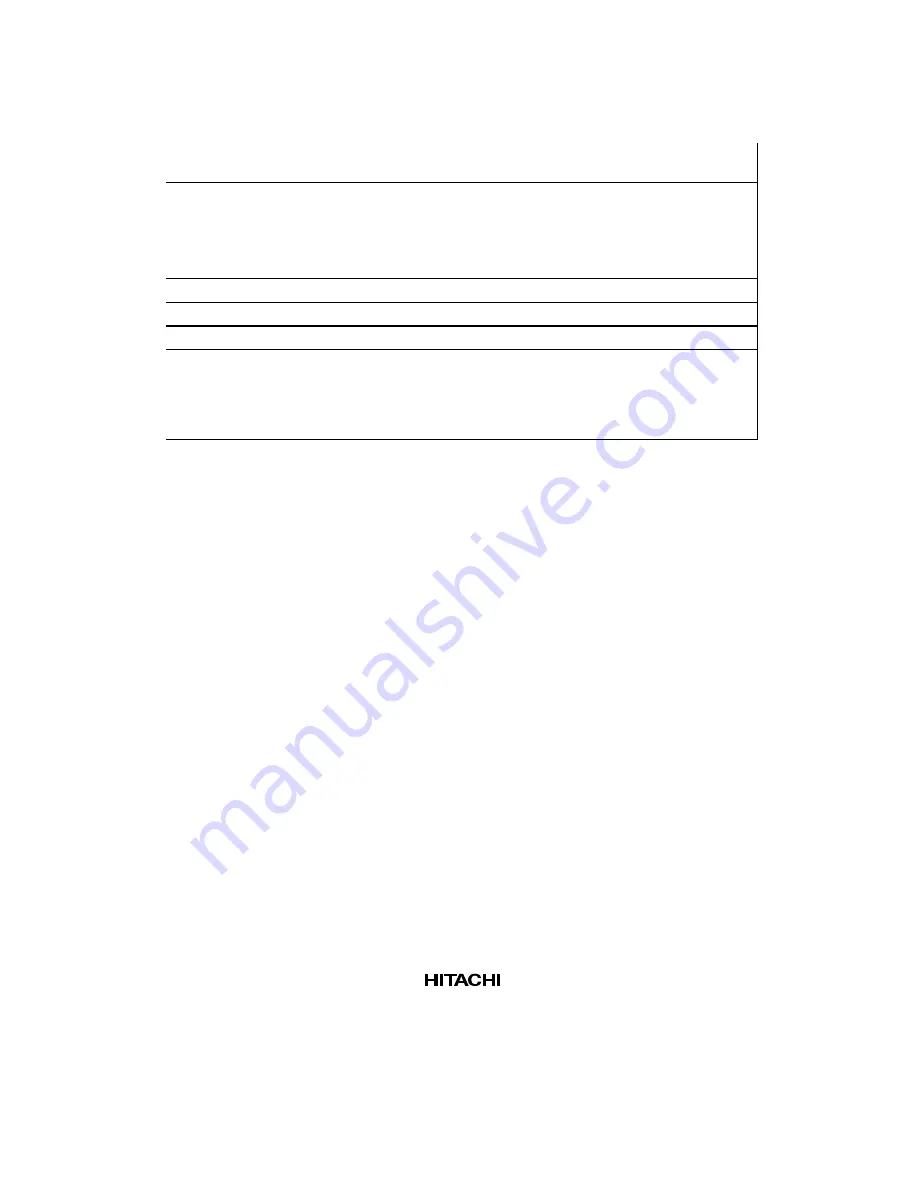

Table 2-2. List of Instructions (7)

Addressing Mode and

Instruction Length (Bytes)

Mnemonic

Operand Size

Operation

#xx: 8/16

Rn

@Rn

@(d:16,Rn)

@–Rn/@Rn+

@aa:8/16

@(d:8, PC)

@@aa

Implied

Condition Code

No. of States

I

H

N

Z

V0

C

XORC #xx:8,CCR

B

CCR

⊕

#xx:8

→

CCR 2

∆

∆

∆

∆

∆

∆

2

NOP

--

PC

←

PC+2

2

-

-

-

-

-

-

2

EEPMOV

--

if R4L

≠

0 Repeat

@R5

→

@ R6 R5+1

→

R5 R6+1

→

R6

R4L-1

→

R4L Until

R4L=0 else next;

4

-

-

-

-

-

-

(4)

Notes: The number of execution states indicated here assumed that the operation code and

operand data are in on-chip memory. For other cases, refer to section 2.5, Number of

Execution States.

(1) Set to 1 when there is a carry or borrow at bit 11; otherwise cleared to 0.

(2) When the result is 0, the previous value remains unchanged; otherwise cleared to 0.

(3) Set to 1 when there is a carry in the adjusted result; otherwise the previous value

remains unchanged.

(4) The number of execution states is 4n + 9, with n being the value set in R4L.

(5) Set to 1 when the divisor is negative; otherwise cleared to 0.

(6) Set to 1 when the divisor is 0; otherwise cleared to 0.

Summary of Contents for H8/300L Series

Page 1: ...H8 300L Series Programming Manual ...

Page 6: ...iv ...

Page 8: ...2 ...

Page 11: ......

Page 14: ......

Page 46: ......

Page 48: ......

Page 60: ......

Page 83: ......

Page 116: ......

Page 150: ...144 ...

Page 151: ......

Page 156: ...150 ...