339

10.3

Operation

10.3.1

Overview

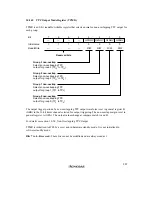

When corresponding bits in PADDR or PBDDR and NDERA or NDERB are set to 1, TPC output

is enabled. The TPC output initially consists of the corresponding PADR or PBDR contents.

When a compare-match event selected in TPCR occurs, the corresponding NDRA or NDRB bit

contents are transferred to PADR or PBDR to update the output values.

Figure 10.2 illustrates the TPC output operation. Table 10.3 summarizes the TPC operating

conditions.

DDR

NDER

Q

Q

TPC output pin

DR

NDR

C

Q

D

Q

D

Internal

data bus

Output trigger signal

Figure 10.2 TPC Output Operation

Table 10.3

TPC Operating Conditions

NDER

DDR

Pin Function

0

0

Generic input port

1

Generic output port

1

0

Generic input port (but the DR bit is a read-only bit, and when compare

match occurs, the NDR bit value is transferred to the DR bit)

1

TPC pulse output

Sequential output of up to 16-bit patterns is possible by writing new output data to NDRA and

NDRB before the next compare match. For information on non-overlapping operation, see

section 10.3.4, Non-Overlapping TPC Output.

Summary of Contents for H8/3060

Page 10: ......

Page 16: ......

Page 114: ...66 ...

Page 132: ...84 ...

Page 144: ...96 ...

Page 170: ...122 ...

Page 212: ...164 ...

Page 268: ...220 ...

Page 332: ...284 ...

Page 396: ...348 ...

Page 494: ...446 ...

Page 698: ...650 ...

Page 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Page 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Page 810: ...762 ...

Page 994: ...946 ...